# JAWAHARLAL NEHRU TECHNOLOGICAL UNIVERSITY: KAKINADA KAKINADA – 533 003, Andhra Pradesh, India DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

| III Year - II Semester | L | T | P | C |

|------------------------|---|---|---|---|

|                        | 3 | 0 | 0 | 3 |

| VLSI DESIGN            |   |   |   |   |

#### **OBJECTIVES:**

### The main objectives of this course are:

- To learn the MOS Process Technology

- To understand the operation of MOS devices

- Understand and learn the characteristics of CMOS circuit construction.

- Describe the general steps required for processing of CMOS integrated circuits.

- To impart in-depth knowledge about analog and digital CMOS circuits.

### UNIT-I:

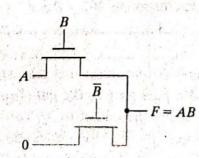

**INTRODUCTION AND BASIC ELECTRICAL PROPERTIES OF MOS CIRCUITS:** VLSI Design Flow, Introduction to IC technology, Fabrication process: nMOS, pMOS and CMOS. I<sub>ds</sub> versus V<sub>ds</sub> Relationships, Aspects of MOS transistor Threshold Voltage, MOS transistor Trans, Output Conductance and Figure of Merit. nMOS Inverter, Pull-up to Pull-down Ratio for nMOS inverter driven by another nMOS inverter, and through one or more pass transistors. Alternative forms of pull-up, The CMOS Inverter, Latch-up in CMOS circuits, Bi-CMOS Inverter, Comparison between CMOS and BiCMOS technology, MOS Layers, Stick Diagrams, Design Rules and Layout, Layout Diagrams for MOS circuits

### UNIT-II:

**BASIC CIRCUIT CONCEPTS:** Sheet Resistance, Sheet Resistance concept applied to MOS transistors and Inverters, Area Capacitance of Layers, Standard unit of capacitance, some area Capacitance Calculations, The Delay Unit, Inverter Delays, driving large capacitive loads, Propagation Delays, Wiring Capacitances, Choice of layers.

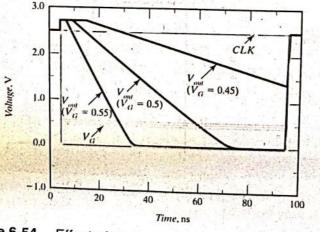

**SCALING OF MOS CIRCUITS:** Scaling models and scaling factors, Scaling factors for device parameters, Limitations of scaling, Limits due to sub threshold currents, Limits on logic levels and supply voltage due to noise and current density. Switch logic, Gate logic.

### UNIT-III:

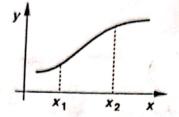

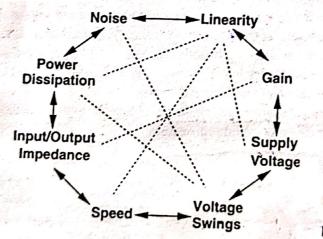

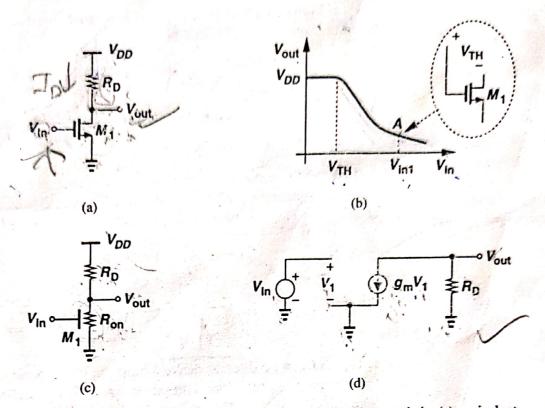

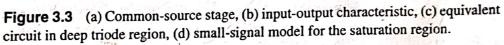

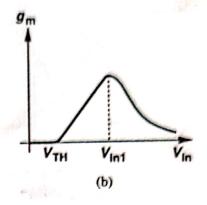

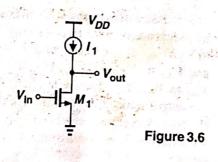

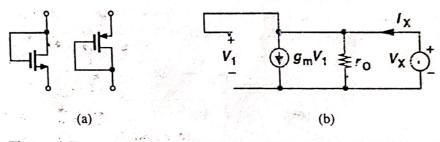

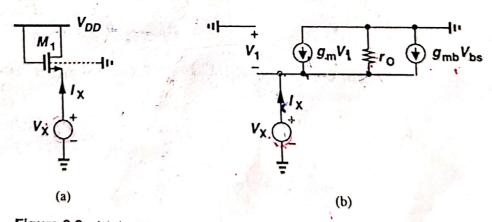

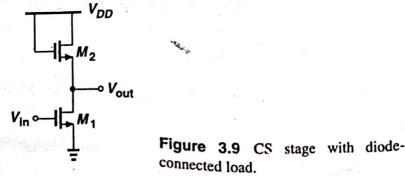

**BASIC BUILDING BLOCKS OF ANALOG IC DESIGN:** Regions of operation of MOSFET, Modelling of transistor, body bias effect, biasing styles, single stage amplifier with resistive load, single stage amplifier with diode connected load, Common Source amplifier, Common Drain amplifier, Common Gate amplifier, current sources and sinks.

### UNIT-IV:

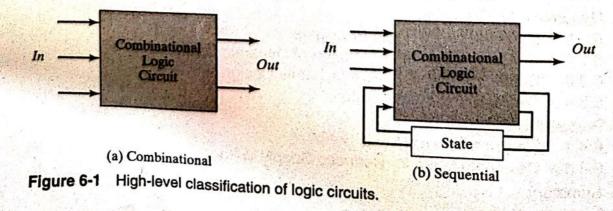

### CMOS COMBINATIONAL AND SEQUENTIAL LOGIC CIRCUIT DESIGN:

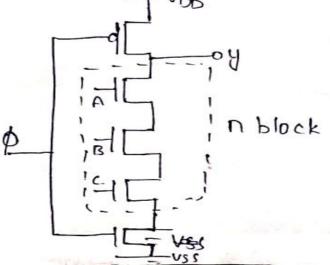

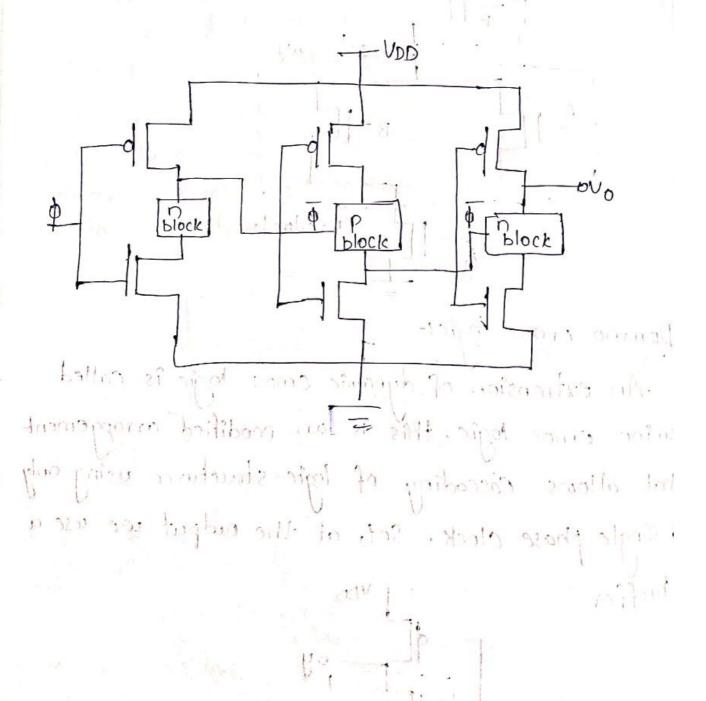

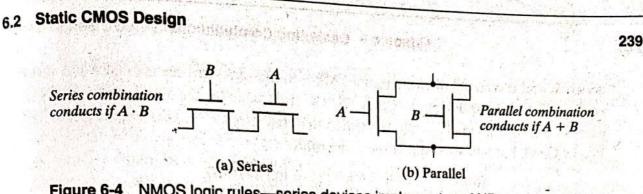

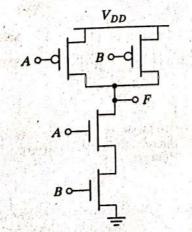

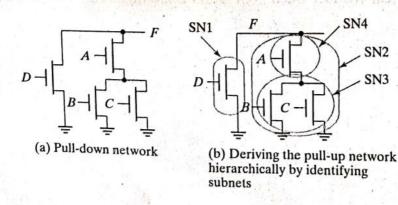

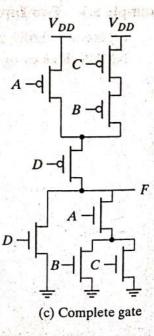

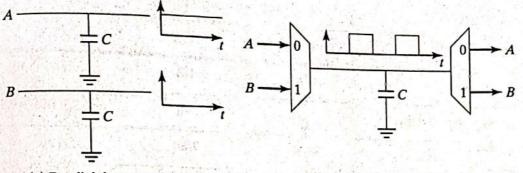

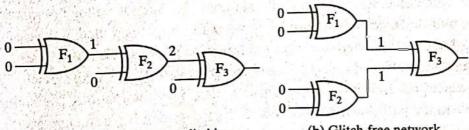

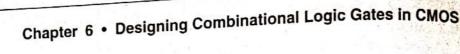

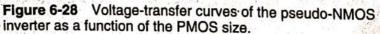

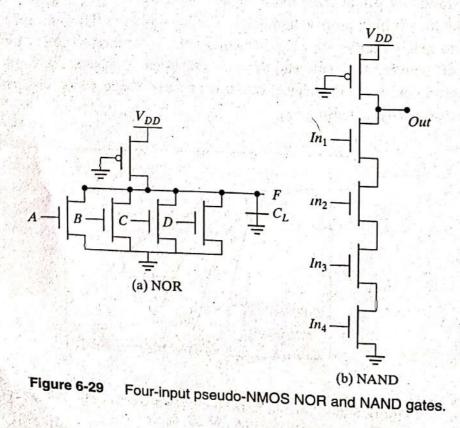

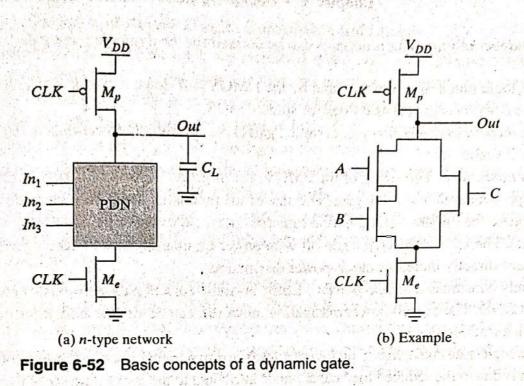

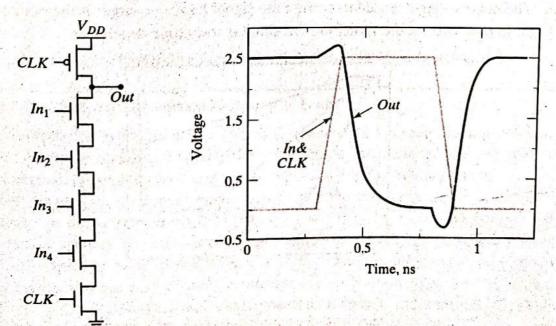

**Static CMOS Design:** Complementary CMOS, Rationed Logic, Pass-Transistor Logic. **Dynamic CMOSDesign:** Dynamic Logic-Basic Principles, Speed and Power Dissipation of Dynamic Logic,

Issues in Dynamic Design, Cascading Dynamic Gates, Choosing a Logic Style,

# JAWAHARLAL NEHRU TECHNOLOGICAL UNIVERSITY: KAKINADA KAKINADA – 533 003, Andhra Pradesh, India DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

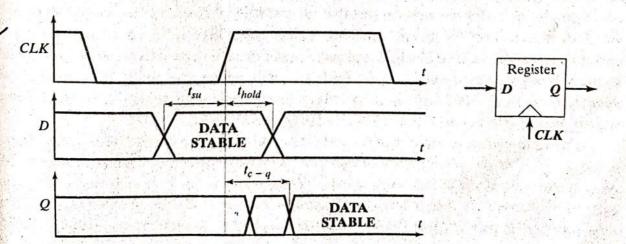

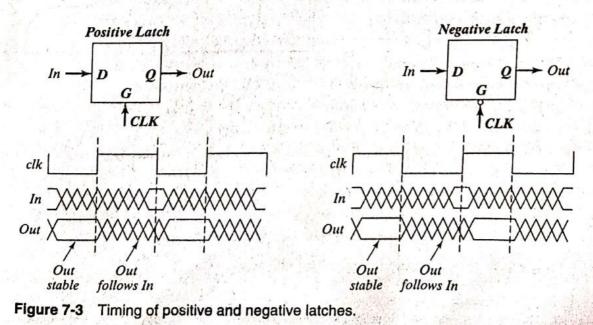

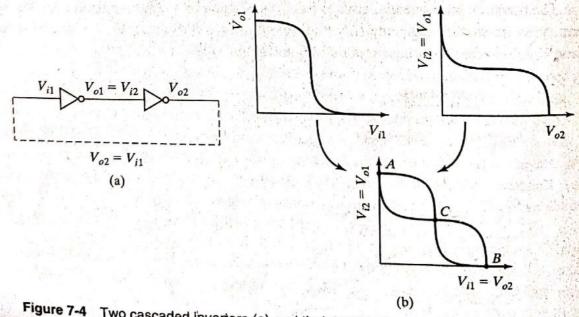

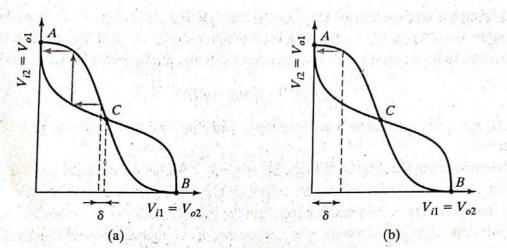

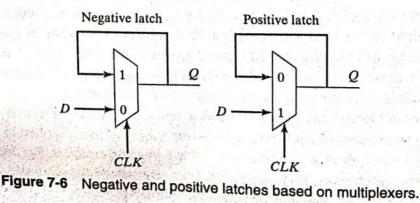

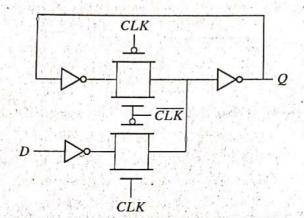

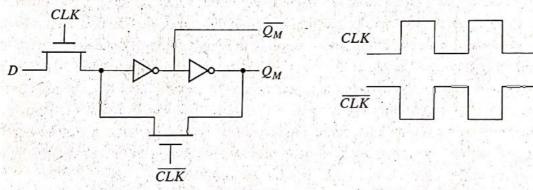

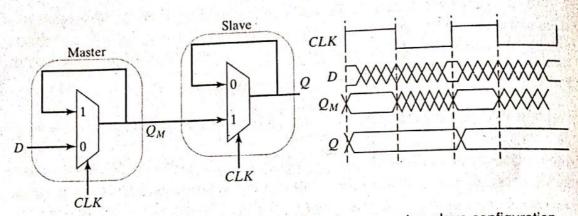

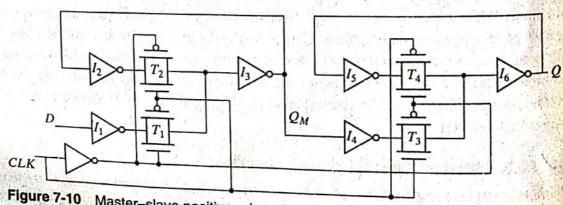

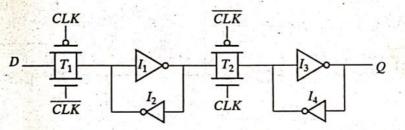

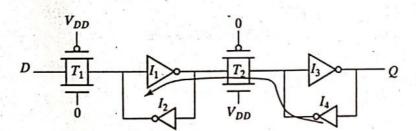

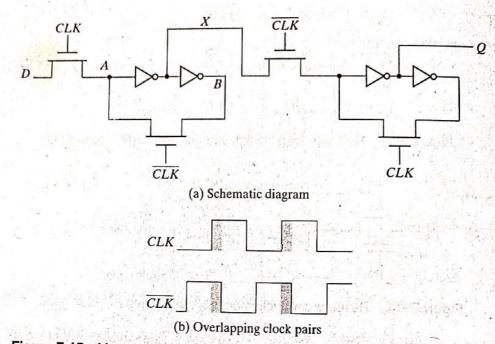

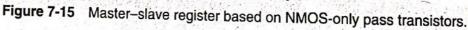

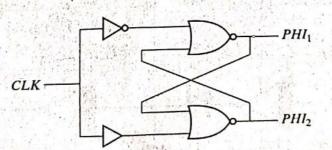

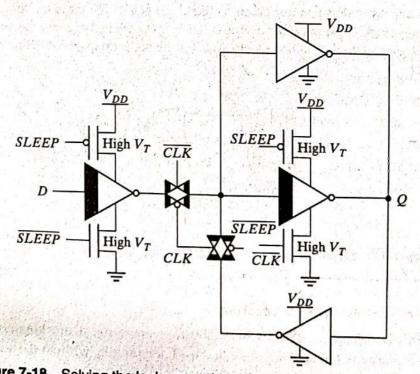

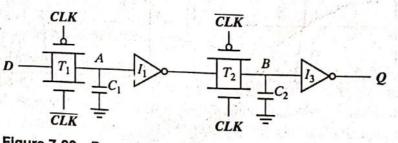

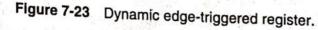

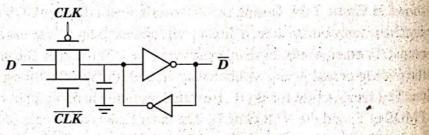

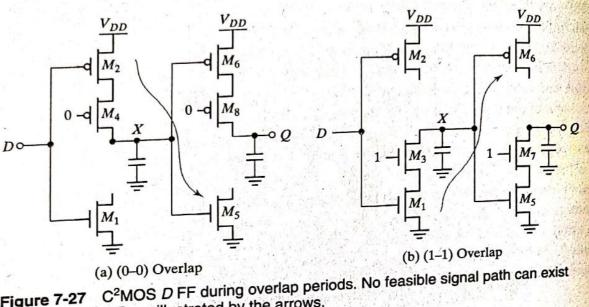

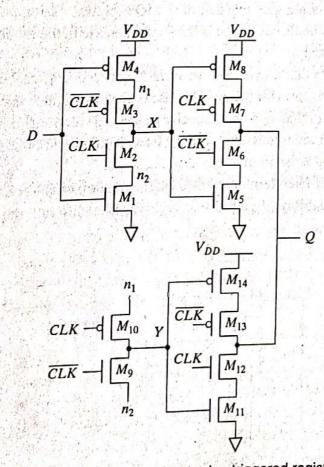

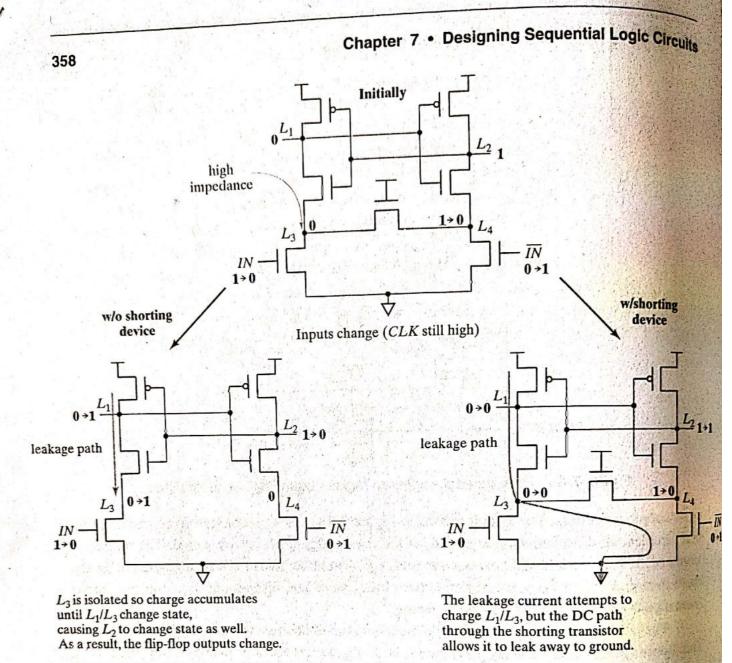

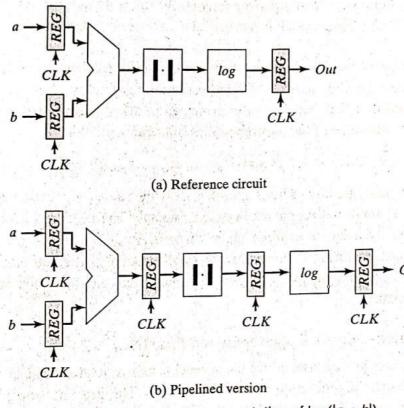

Gate Design in the Ultra Deep-Submicron Era, Latch Versus Register, Latch based design, timing decimation, positive feedback, instability, Metastability, multiplexerbased latches, Master-Slave Based Edge Triggered Register, clock to q delay, setup time, hold time, reduced clock load master slave registers, Clocked CMOSregister. Cross coupled NAND and NOR, SR Master Slave register, Storage mechanism, pipelining

### UNIT-V:

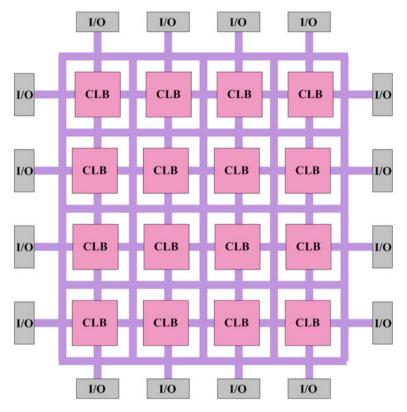

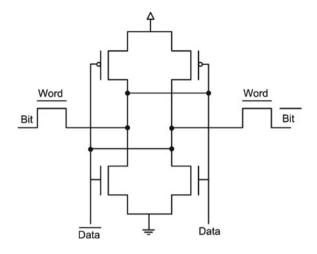

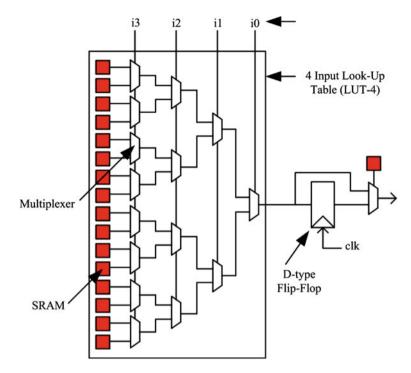

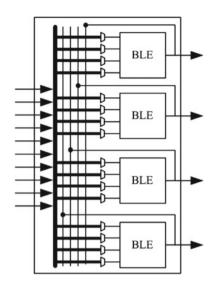

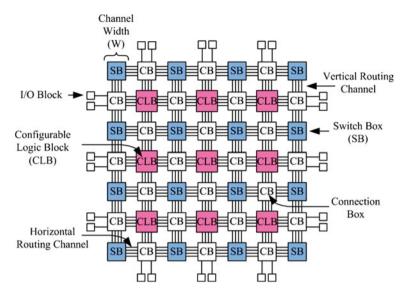

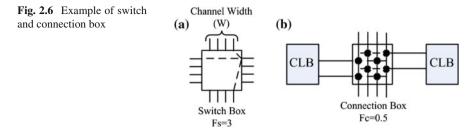

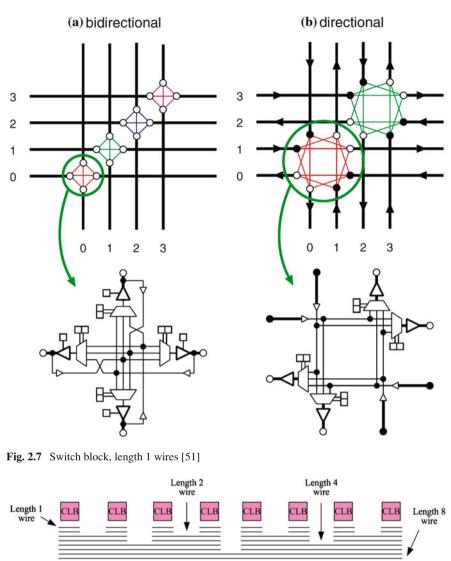

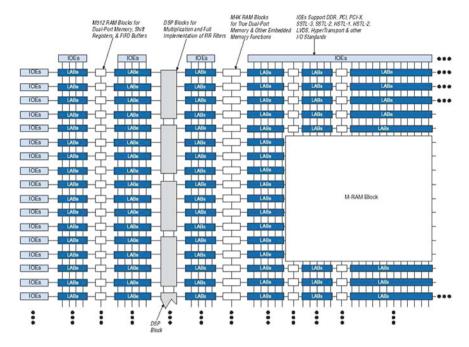

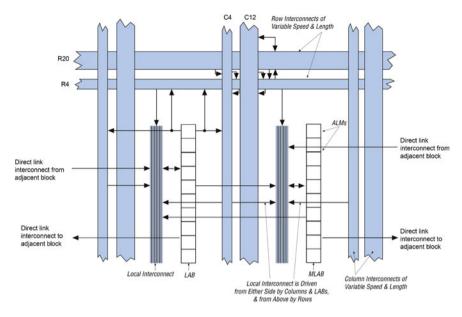

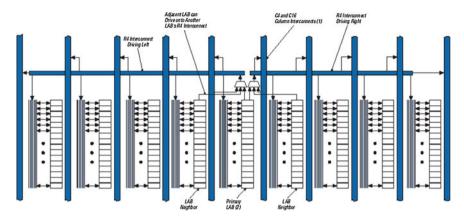

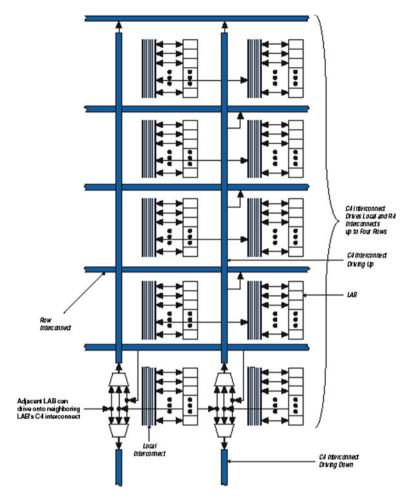

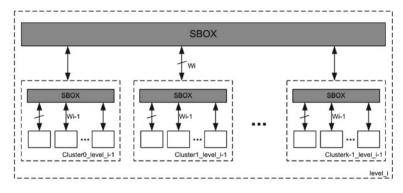

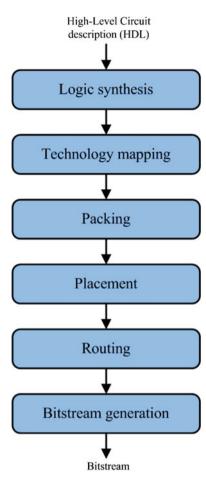

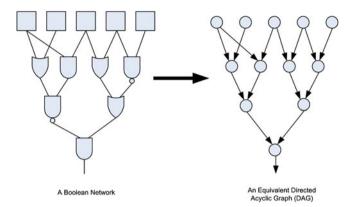

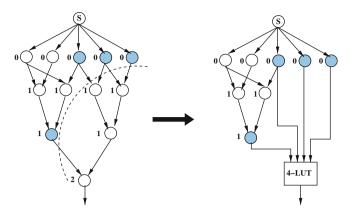

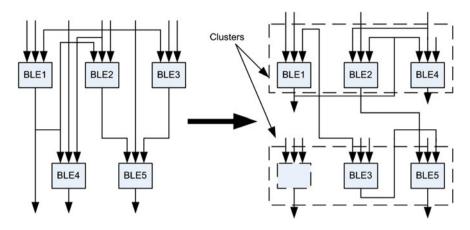

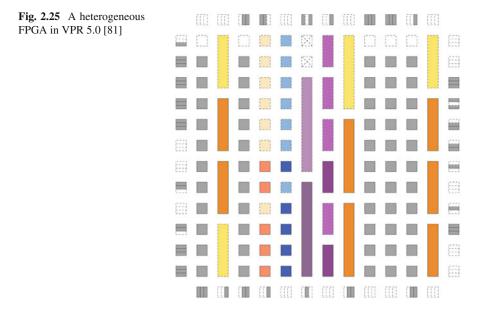

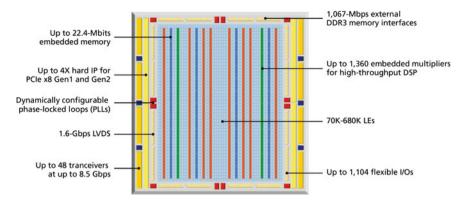

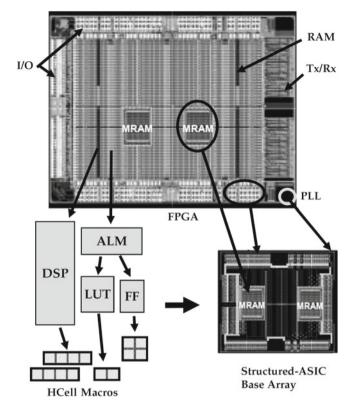

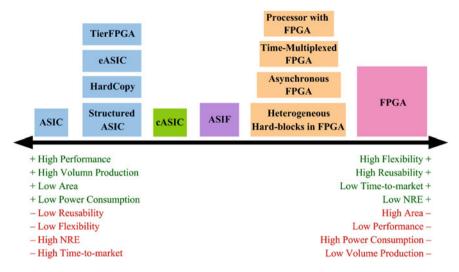

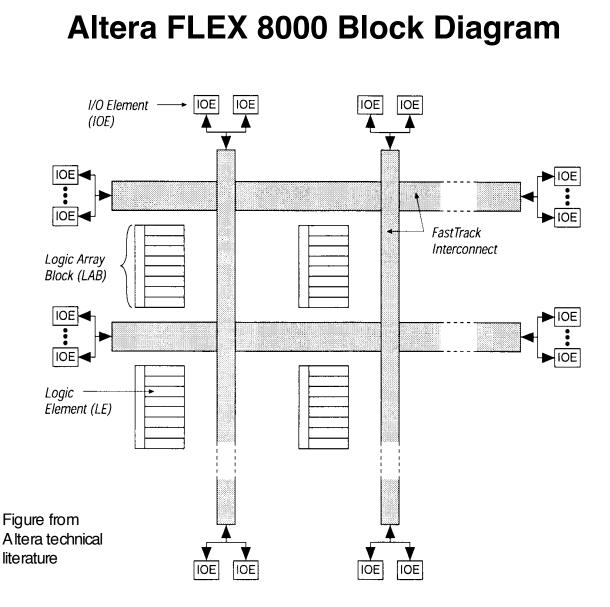

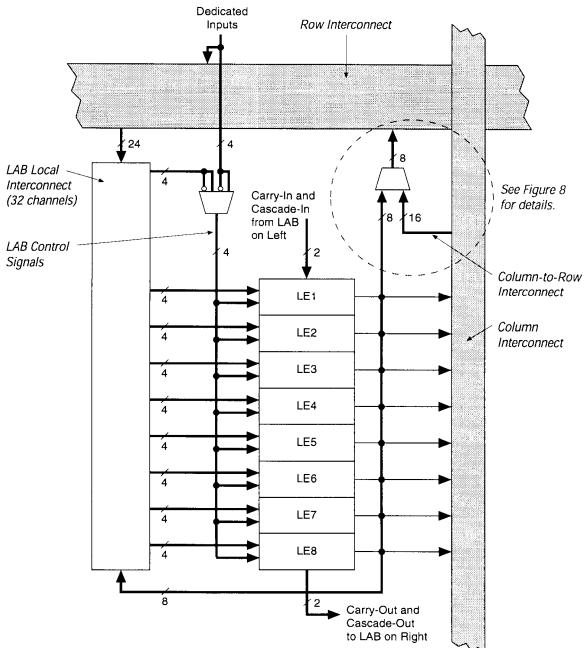

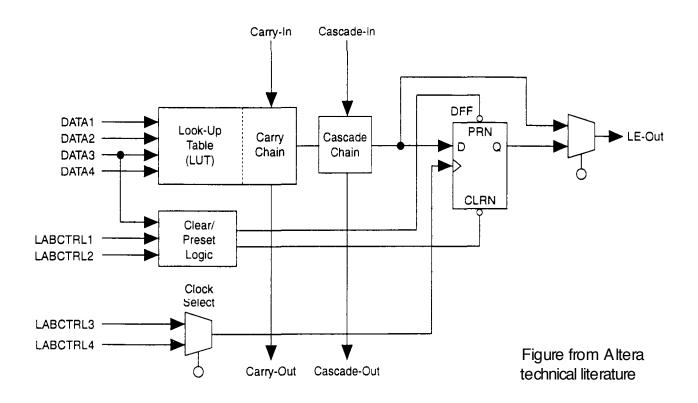

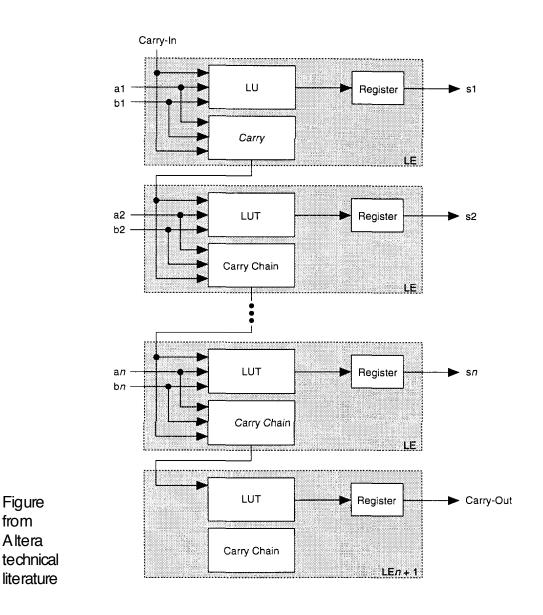

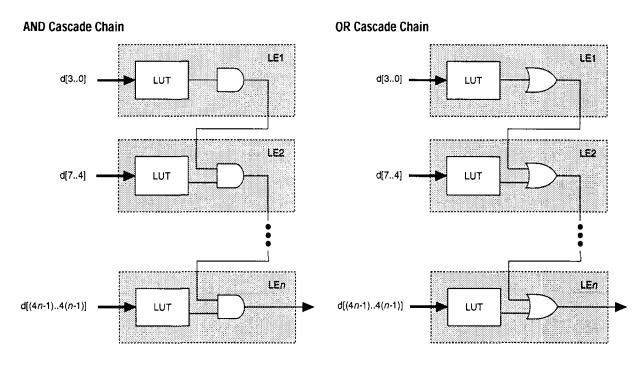

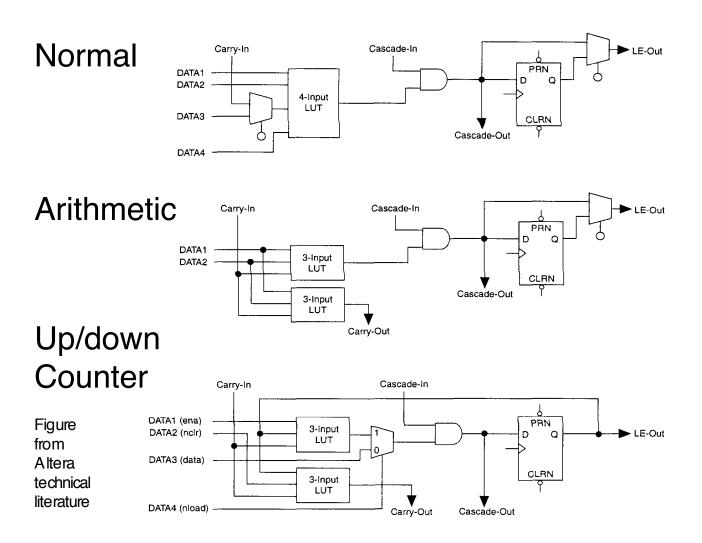

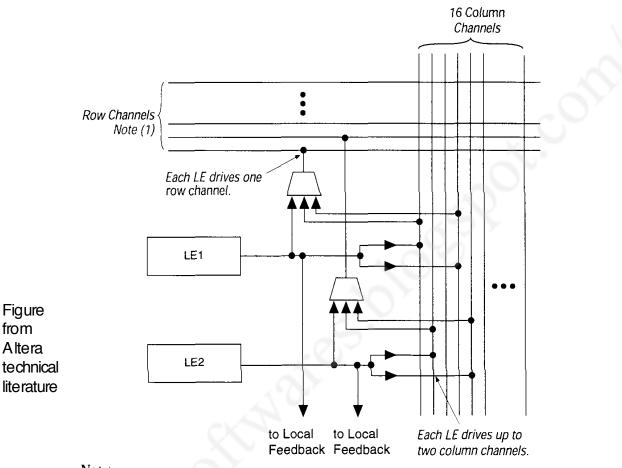

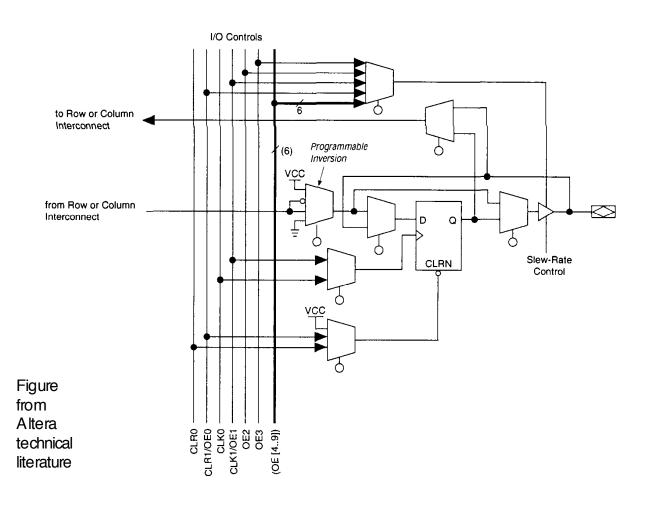

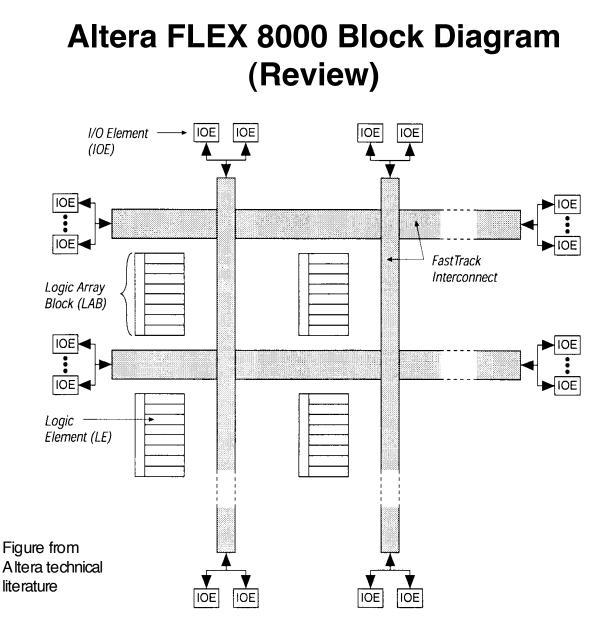

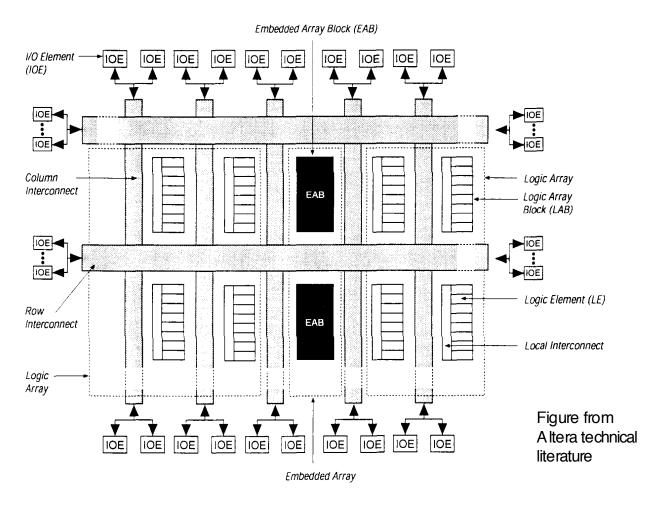

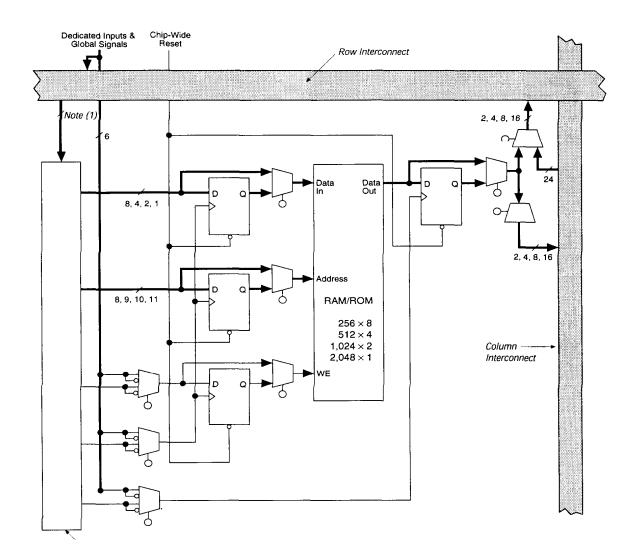

**FPGA DESIGN:** FPGA design flow, Basic FPGA architecture, FPGA Technologies, Introduction to FPGA Families.

**INTRODUCTION TO ADVANCED TECHNOLOGIES:** Giga-scale dilemma, Short channel effects, High–k, Metal Gate Technology, FinFET, TFET.

### **TEXTBOOKS:**

- 1. Essentials of VLSI Circuits and Systems Kamran Eshraghian, Douglas and A. Pucknell And SholehEshraghian, Prentice-Hall of India Private Limited, 2005 Edition.

- 2. Design of Analog CMOS Integrated Circuits by BehzadRazavi, McGraw Hill, 2003

- 3. Digital Integrated Circuits, Jan M. Rabaey, Anantha Chandrakasan and Borivoje Nikolic, 2<sup>nd</sup> edition, 2016.

### **REFERENCES:**

- 1. "Introduction to VLSI Circuits and Systems", John P. Uyemura, John Wiley & Sons, reprint 2009.

- Integrated Nanoelectronics: Nanoscale CMOS, Post-CMOS and Allied Nanotechnologies Vinod Kumar Khanna, Springer India, 1<sup>st</sup> edition, 2016.

- 3. FinFETs and other multi-gate transistors, ColingeJP, Editor New York, Springer, 2008.

### **OUTCOMES:**

### At the end of this course the student will be able to:

- Demonstrate a clear understanding of CMOS fabrication flow and technology scaling.

- Apply the design Rulesand draw layout of a given logic circuit.

- Design MOSFET based logic circuit.

- Design basic building blocks in Analog IC design.

- Analyze the behaviour of amplifier circuits with various loads.

- Design various CMOS logic circuits for design of Combinational logic circuits.

- Design amplifier circuits using MOS transistors.

- Design MOSFET based logic circuits using various logic styles like static and dynamic CMOS.

- Analyze the behaviour of static and dynamic logic circuits.

# UNIT - 1

Introduction & Basic Electrical Properties of Mos exts:-VIST - Very Large Scale integration Definition of Ic:-

an well be plad in

To is an electronic for integrated circuit and may be given as combination of active of possive. elements that are integrated on signle silicon chip. As there are Several advantages of using Silicon which includes, if acts as good insulating material, Oxiding material.

Ave made using silicon only [i.e., 90.1.] Trends in Micro electronics:-

The electronics now a days available in the market are categorized by reliability, Size, weight, Volume, cost.

In addition these the VISI technology made an advantage to have a more powerful & flexible processor for availing a good source.

\* The BJT was first invented by william shockley & John barden in 1947 at bell laborataries.

\* up to 1950's the BJT technology was dominated by vaccum tubes.

\* The 1st Ic technology was developed in 1960's and there by a revolutionary come into the electronics industries.

1

Symbols of Mosfer:-1 11-1) and the fail of the state of the second VISI Technology BJT Hosfer . to to ma n-channel P-channel sho li Depletion enhance Depletion - ment mode mentmode mode mode so wail place assilt price above so N-Mos P.Mor <u>G</u>\_\_\_\_\_ <u>L</u>\_\_\_\_ <u>L</u>\_\_\_\_ <u>L</u>\_\_\_\_ <u>L</u>\_\_\_\_ <u>L</u>\_\_\_\_ <u>L</u>\_\_\_\_ <u>L</u>\_\_\_\_ <u>L</u>\_\_\_\_ <u>M</u>\_\_\_\_ <u>M</u>\_\_\_ <u>M</u>\_\_\_\_ <u>M</u>\_\_\_ <u>M</u>\_\_\_\_ <u>M</u>\_\_\_ <u>M</u>\_\_\_\_ <u>M</u>\_\_\_ <u>M</u>\_\_\_\_ <u>M</u>\_\_\_\_\_ <u>M</u>\_\_\_\_\_ <u>M</u>\_\_\_\_\_ <u>M</u>\_\_\_\_\_ <u>M</u>\_\_\_\_\_ <u>M</u>\_\_\_\_ <u>M</u>\_\_\_\_ <u>M</u>\_\_\_\_\_ <u>M</u>\_\_\_\_\_ <u>M</u>\_\_\_\_\_ <u>M</u>\_\_\_\_\_ <u>M</u>\_\_\_\_\_ <u>M</u>\_\_\_\_ <u>M</u>\_\_\_\_ <u>M</u>\_\_\_\_ <u>M</u>\_\_\_\_ <u>M</u>\_\_\_\_ <u>M</u>\_\_ Gid Depletion mode · O mark De current. lorn's init: BJT is a Current Controlled device where as Mosfet is a Voltage Controlled dévice. In r substantiant instantials

2

Level's of integration:- in the time is mind have Depending upon the complexity of integrated CKE the classification Can be given as SSJ (Small Scale integration) - 10 to 100 MS.I ( Medium Scale integration) - 100 to 1000 -ISI (large Scale integration) - 1000 to 105 ULSI (very large scale integration) - 105 to 10 strain all al The upcoming technology i.e., ULSI (ultra large scale integration) - 10 to 100 Difference Between BJT and MOSFET. MOSFET 2 BJT 1. It is Voltage control 1. It is current control dévice. device. D. Droin and Source a. collector and emitter terminals ore interchange. -lerminal's are not inter 3. 3. Ompédance is high. change. 3. Impedance is low. 4. Ilp Impedance is high 4. Ilp Impedance, is low 5. Gransconductance is 5. Trans conductance is, il tow wid give the busil information ballen hìgh. \* Why it is called FET? A) GID Vgs = Voltage blue gate and source Vgs ]s terminols. By the external application of vgs they is an electric field development blus gate and source .

3

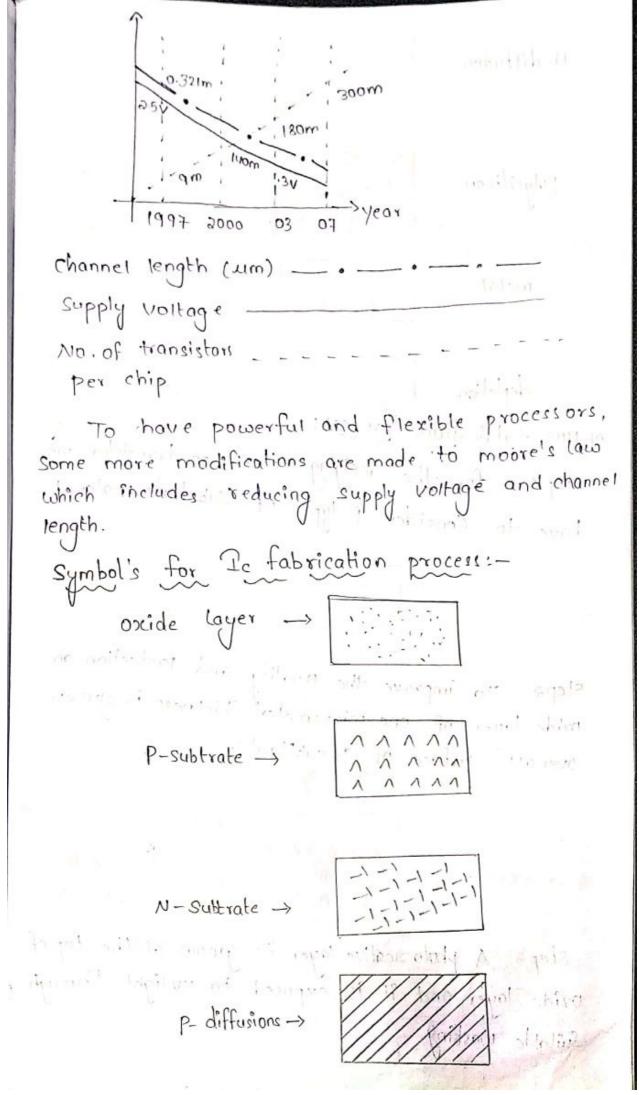

and hence it will get effected in correspondy with vgs. Hence it is called field effect Transistor (FET). The IC EJIA:-\* The first Ic emerged in the early 1960's. \* Depending upon the potential of that Ic. we Can find no of transistors that are being integrated in the single silicon chip. \* In less than 3 decodes the no of transistors count has rasin form loo to loop millions of transistors per chip. No of transistors per chip 10,000m 1000mtoom . (Om m 1997 2000 2003 2007 Moore's low: -The graphical Depresentation that gives the relation - ship blu the year. V/s no. of transistor per chip is called moora's law. No of transistors supply channel per chip voltage length lum) 30 0.3 10000m 0.25 2.50 1000m 1.5V U.I. toom iom ' Im

www.Jntufastupdates.com Scanned by CamScanner

5

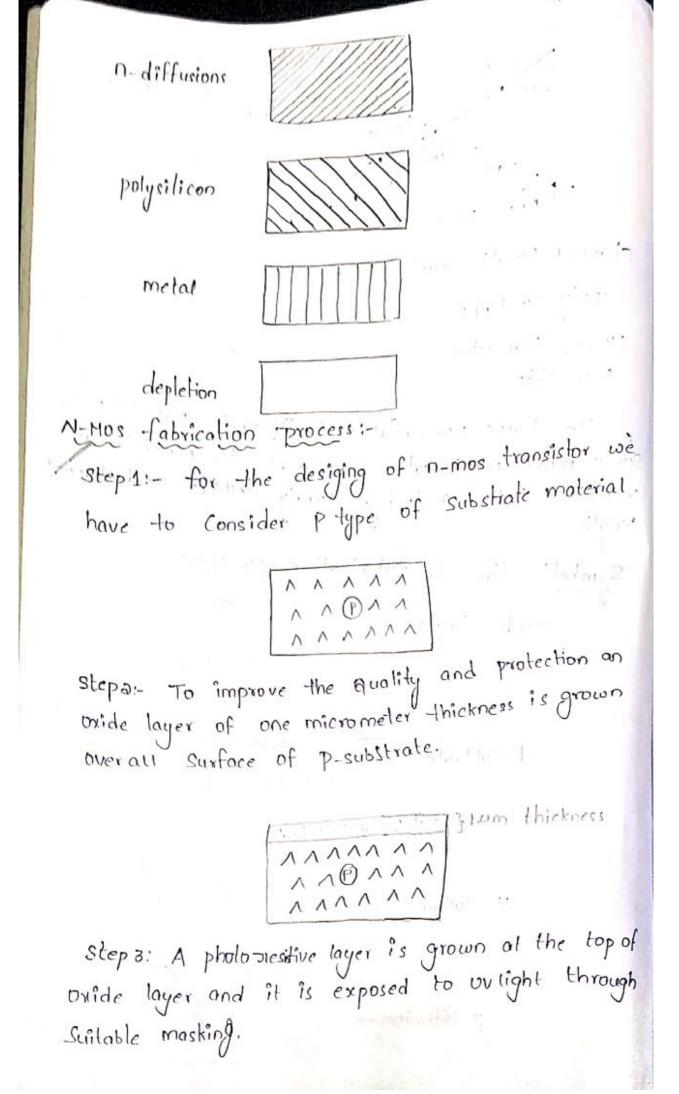

+ + to to to to voy 3-14m thickness  $\frac{1}{2} = \frac{1}{2} = \frac{1$  $\wedge \wedge \wedge \wedge \wedge$

step 4:- The uncovered portio. of mask allows uv light to flow through it, the oxide layer will be get softened and Jumain Covered position will be remain harden.

and the process is Called "Etching"

New March

7

| 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1                                                  | the promition the first |

|-------------------------------------------------------------------------------------------|-------------------------|

| $\wedge$ | in alman i ama          |

|                                                                                           | and the second          |

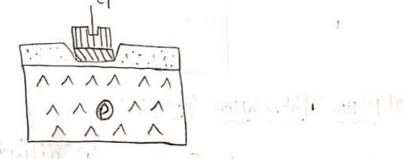

Step 5:- An oxide layer of orlum thickness is grown and using polysilicon and metal gate terminal can be extracted.

Step 6: To diffuse n-type of impurities into p-type of substrate the masking and Etching processes are again Carried Out

Stepting The uncovered portions of mask will be get softend and their by surmoved using Etching Process. The n-type of impusities are diffused into the P-type of Substrate as shown below. 1994 in the through it is a point of i the within the many of the A A B A A A A A A A A A steps:- From the n-type of impurities drain and Source terminale Source terminals can be extracted using polysilicon ond metals. ~ ~ ~ ~ ~ ~ ^ ~ ~ ^ ~ ~ ~ ~ ~ ~ ~ 0) P-Mos fabrication Process:-P-Q-P P-diffusion Substrate step 1:- for the designing of P. Mos transistor we have to consider n-type of substrate materials mine -1-1-1-1--1-1-01-1--1-1-

step 2:- To improve the quality and protection on oxide layer of lum thickness is grown overall surface of n-substrate. Jum thickness -1-10-1-1--1-10-1-1-1-100 14-1step3:- A photoresistive loyer is grown at the top of oxide loyer and it is exposed to uv light through Suitable Masking. 1 J. J. J. J. J. Wrays -> photoresistivity -1-1-101-1-1-1 -1-1-1-1-1-step 4:- The uncovered position of mask allows uv light to flow through itr the oxide layer will get soften and giemain covered portion will remain harden. The portion which is soften will be removed and this process is called Etching. Step51- An Oscide layer of Orlum thickness is grown and using polysilicon and metal gate terminal can be exerted.

C Dais steps:- To diffuse p-type of impunities into n-to of substrate - the Masking and eteching process ar again Carried out. G WWW 01-1-1-1 Step 71- The uncovered portion of Mask will be get soften and there by removed by using "Etching" Process. The n-type of impurities are diffused into P-type of substrate as shown in below. 1-1-101-1-1--P P-1-1-1-1-1 steps:-from the p-type of impurities drain and Source terminale can be extracted by using polysilium and metals.

CHOS - Investor --\* CHOS is known as complementary metaloxide semi -totion and it will produce output has complemen -tation of input. -\* The CHOS can be designed with the help of PHOS \* NHOS transiston are faster than pmos devices because the Hobility of electrons are greater. compare to Mobility of holes. i.e., en = a.5up CHOS Invertor Circuiti-- Vpp Vin Vo/p Q, 92 BI \_\_\_\_ Demargation D DN OFF 1 OFFLON -ovb/p 1 D 92 GND operation :-Case (1): - when Vin is Zero when the input is logic o then the transistor Q, Will get on, Q2 will get off there by producing Vo ai logic'i. Case (2): - when Vin is logic 1.

When the Input is logic 1 then Q, will get turn Off, Q2 will get turn on, tence the Vo as logic'o!

fabrication of crossfor the fabrication of CMOR we have different Types 1. Cros using p-well process D. Cros using N-well process 3. Twin - Tub process Chos fabrication wing N-well processistep 1:- for the designing of CMOS using N-were process we have to consider a p-type of substrate. step 21- Diffuse N-type of substrate (N-well) into p-type of substrate. A A A A A steps:- grow oxide layer on the surface of p-type Substrate of Lum thickness Vic Mi India 1 A A A A TOTT Flum thiox A A A A A A

I av a tar a 1. 1. n-type and p-ty Steps:- To have diffusions 1 1 14 of MONAN OF OFFICE AAAA AAAAAA Step9: finally Furthere C-Mos the 1/p and olp terminals can be extracted as like shown below. 9 Vin 9VD - 455 Vpp AAAAA T-1-1 ΛΛΛΛΛΛΛΛΛ A A 2) C-Mos fabrication using p-well process:-Step 1: For the designing of C-MOS using P-well process we have to Consider and n-type substrate.

- (-) same n' all' s pol Steps:- diffuse p-type substrate (p-wen) into n-lype of Substrate. Step 3:- grow oxide layer on the surface of P-type of substrate of lum thickness. multiple and the film Stepy:- To improve the protective ness or Photo siesistive layer is grown and it is exposed to uvlight through suitable masking. Photoresistive laye1 1-1-1-1

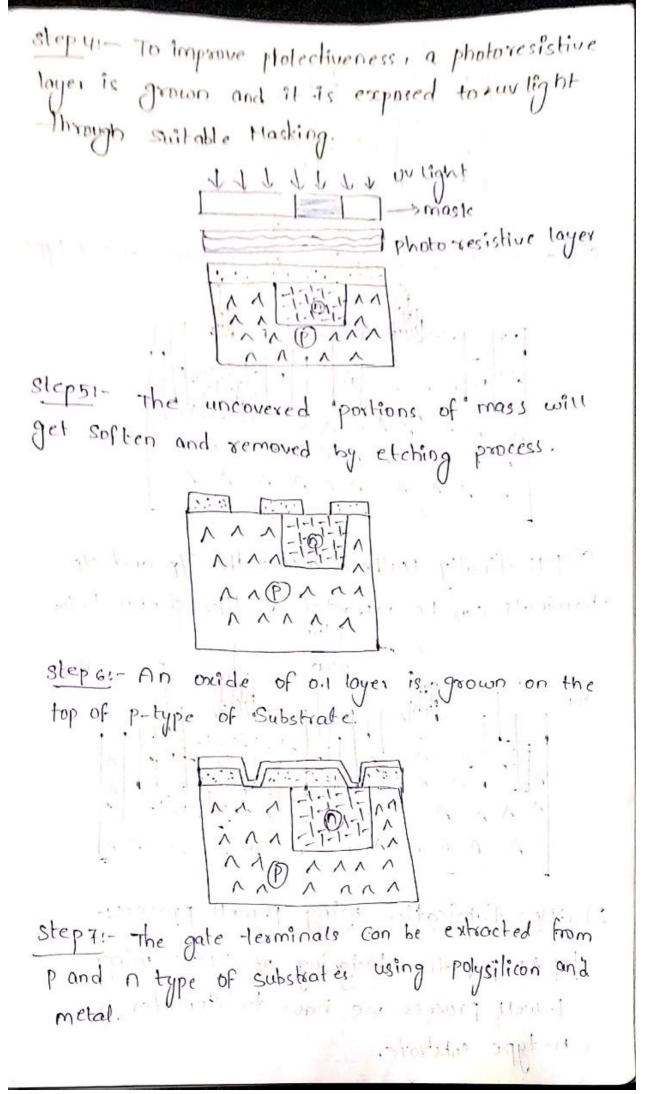

Step 5: The uncovered portions of -maskwill de Soften and removing the " etching process. REAL ONLY CODE A A A -1-1-A A A -1-1-A A A -1-1-Step 61-An oxidé layer of orlum is grown on the top of P-type substrate. AAAA NA.P 2.1. Step 71- The gate terminal can be extracted foom p and n-type of the substrate using Polysilicon Metal I- 1 1 -1-1 -1- 10 1 -1-1 VVV

stepsi- To have diffusion p-type and n-type into Corresponding NE p type of Substrates Repeat -fhe steps from (1) to (6). 6 step 9: finally for the cmos the i/p and o/p terminals extracted as like shown below. 9 Vin VDD 900 USS 0.2 - DIMAN bottont va Section of input inpedence and ,G Diorn had an and had been mind hather was in and it in more silois daine a contribution signed and LOW TO THE bloor all surfleet appropriate all a choid a vale on loor 2 lobrition pathicharing anto none for solution

(Mos fabrication using Twin-Tub process!-Mos using twin - tub process is the logical extension P-well Line desiging Can k of P-well and N-well process. the desiging can be Carrie and N-well process. the desiging can be Carrier out by taking a high mestivitive n-type of Substrated Substrate. Here the design is consider such that The performance the design do not comprise the The performance of p-well do not comprise the Performance of p-well do not comprise the Performance of ri-well using Epitaxial layer. Hence doping level is steadily acheieve. 9 Vin VDD Vss 9 Vout N A(P) sepilaxial layer un : Comparision blu cruos technology and Bipolar technol S.NO Bipolar technology CMOS technology 1. It is a current 1. It is a Voltage controlled controlled device. device. Low input impedance Q. High input impedance and and high output drain low output drain current. Current. 3. Low static power dissipation High static power dissipation 4. Scable threshold voltage threshold voltage may depend on type of Semiconducting materials Parameters. on device

These are essentially uni Bidirectional Capability 5. that is drain and source - directional, had always the ter of terminals Can be inter " change. low transconductance. High transconductonce. 6. 1.e., Im is directly that is Im devin perportional to /impedore Jm & \_\_\_\_\_\_ Impedance. low package density 7. High package density. 8. low Voltage Swing thigh noise margin a pail- 113 levels and that pairs of S Section 2 CAR Enhancement mode Mosper: [nmos] While desinging N-Mos we have to take p-type Substrate and it has two n-type of diffusions to form drain and source. terminals for extracting gate, drain add Source terminals polysillicon and metal contacts are use for necessary deads. Here we have to apply a suitable positive voltage at gate terminal to create channel blue drain -the and Source SIC DELL 10 asila purctional and What TO ballado 1 11 () has the grant is 13/301 and for

19

operation of NMOSI-The designing of Nimos includes Considering a P-type of substrate and to heavily doped nt imput are docc are diffuse into p-type of substrate to get drain and Source and Source terminals. Case (1): -When ygs=ou when vois = ou no channel will be form and no Current Condition takes place. \* Here when Vgs = 0 we can find two junction diodes that are connected in series back to back manner in blue drain and source and these two diodes are in neverse bias Condition. and the second of the second of the it is a second s the second from the second and show hat  $\begin{array}{c} & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\$ (ase (2):- when vgs >0v, means we are applying Some possible voitage at the gate terminal then the majority charge carries in N-mos that is holes will get reppled by an amount of Voltage applied at the gate terminal. \* IF we increase the gate potential step by Step then the holes in the substrate will get www.Jntufastupdates.com Scanned by CamScanner 20

rippled and pushed down leaves a depletion region blu drain and Source. Hence it is called charge Inversion layer. In the start of antiat the tomoto to the tev not \* After having a charge inversion layer the holes in the gale terminal will get attracted to not diffusions present in droin and source Terminals, Thereby forming N-channel blue drain and Source. \* Alote: - The voltage at which charge inversion layer forms and the gate terminal can be inverted is called therehold voltage of mass device. Asi G' D . . . . . . . . . . . . . . . . and the set of the set and man by Ann O ANN is to the cage (3):- when vgs ZVE , VDS = 0. No channel will be form and hence no current Conduction takes place i.e., Pos=0 Case (4): - Vgs > VE, VDS = 0 When Vgs > Vt then Channel will be form but no current Conduction takes place i.e., Culloff Jegion. Jegion. Active region -> current conduction takes place

Saturation Diegion -> Acts as constant current source Case(5):- when vgs >VL, Vds EVg all grantest When Vgs >ve channel will be form, when UDS = Ug (VDS = Ugs - VE) - then near drain terminal Their is an insufficient electric field and it is in non-saturation Condition. G Promin 1 no wint S The state of the second state 20.00 pinch off 111 pollo 2 Section 1. A A A A A A mahert NAN ONNAN Case (G):- when. vgs >Vt, Vds >vg When Vgs > Vt, Vds > vg (vds > vgs - Vt) then channel Will be form and as vos as raised greater than Vgs-Vt their is insufficient electric field near the drain terminal which causes the channel NO Channel UNI pinchoff Condition share page the notion 20V ( -: (P) -: (P) -> pinch off NANA Corrend of n n nD Solve Bregion & Current Coursellon Make

Here when Vgs7Vt, Vds7Vgs-Vt it is in Saturation mode and hence acls as constant current Source. Nole:- for an enhancement mode n-most the without will be created by opplying positive channel will be created by opplying positive Voltage at the gate terminal. \* IF It IS p-Mos, to create channel we need to apply negative voltage at the gate terminal.

Depletion Mode N-MOS:-In Depletion mode MOSFET It is having an inbuilt channel that is no need to apply External Voltage.

In this depletion mode nomos the channel will be created blue drain and source prior to Manufactoring stage before applying insulating and metals.

ed much author of

- muss bao alorb

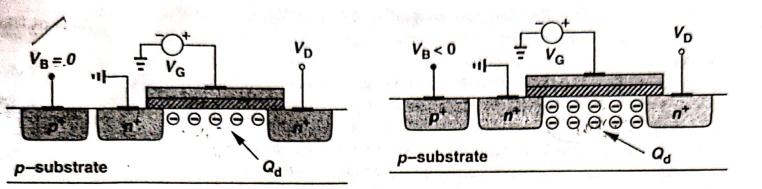

Body Mass effect:-Note:- Depletion mode N-mos is always ON. If you Want to remove channel, we need to apply the Negative voltage at the gate terminal.

for N-mos, basically the source voltage and Body Mass Effect :-Body potential should be equal that is Vs=VB. If VB==0 i.e., It is having some in built possible Potential thon it couses an effect on these should in include it includes an effect of the lower is included it includes the second second in the second sec Voltage hence threshold voltage level is increase to available threshold voltage to avoid this the body is connected to suitable. Nearly negative voltage w.r. to source hence this effect is called Body Mass effect.  $d \to d \to \pi$ G P AN ANDANA A AAAAAA VBB Relationship blue Ids Us Vds :-The whole concept of mass transistor revolves the application of Vgs which inturn causes to «Create a channel blw drain and source. : The current Ids is a dependent on both Vgs Morrow Depletion proje Dunes " an and Vas. " on sub-land Service veltage at the gale 's miner.

The current Ids can be given by  $\Box_{d3} = - \Box_{sd}$  $: I_{ds} \simeq \frac{Q_c}{\widetilde{L}_{de}} \longrightarrow (1)$ where Rc is charge and Tas is electron transit time we know that  $T_{dS} = \frac{L}{V} \longrightarrow (2)$ where L= length of the channel and V = Velocity The velocity 'v' can be given as  $U = \mathcal{U}(\mathbf{E}_{ds} \rightarrow (3))$ where is called mobility constant Eds = Effective electric field b/w drain and source.  $E_{ds} = \frac{V_{ds}}{L} \longrightarrow (4)$ Sub () in (3)  $V = u \frac{V_{dS}}{J} \longrightarrow (5)$ Sub 6 in 2 - bill of hair and  $ds = \frac{L}{19}$  $T_{ds} = \frac{L}{\mu V_{ds}} + V - (V - 2V) = 0$  $\gamma_{ds} = L^2 / \mu V_{ds} \rightarrow (6)$

Sub (c) in (c)

$$T_{ds} = \frac{Q_{c}}{Y_{ds}}$$

$$T_{ds} = \frac{Q_{c}}{W_{ds}}$$

$$Case(j) = Non - Saturation$$

when it is in non - Saturation then the effective

when it is in non - Saturation then the effective

woltage is  $\frac{V_{ds}}{2}$ .

The charge  $Q_{c}$  can be given as

$Q_{c} = Eg E_{0} E_{ins} w L \longrightarrow (i)$

wheshe  $E_{g}$  is effective gate voltage

$E_{0}$  is permittivity of free space

$E_{0} = 8 \cdot 854 \text{ xib}^{2} F/m$

$E_{ins} = Jelative Permittivity$

$E_{ins} = 4 (for silicon)$

$w = width$

$W = W_{ds} - Vt$

$E_{g} = [(V_{gs} - V_{t}) - \frac{V_{ds}}{2}]$

$Where D = 0xide thickness$

$$\begin{aligned} & \text{Re} = \left[ \left( V_{\text{A}} s - V_{\text{E}} \right) - \frac{V_{\text{A}} s}{2} \right] \text{ So Eins usl.} \\ & \text{Re} = \left[ \left( V_{\text{A}} s - V_{\text{E}} \right) - \frac{V_{\text{A}} s}{2} \right] \frac{\mathcal{E} \circ \mathcal{E} \text{ins usl.}}{D} - \mathcal{I}^{(3)} \\ & \text{WKT} \end{aligned} \\ & \text{Ids} = \left( \frac{1}{\sqrt{3}} s - V_{\text{E}} \right) - \frac{V_{\text{A}} s}{2} \right] \frac{\mathcal{E} \circ \mathcal{E} \text{ins usl.}}{D} \frac{1}{\sqrt{\sqrt{3}}} \\ & \text{Ids} = \left( \left( V_{\text{A}} s - V_{\text{E}} \right) - \frac{V_{\text{A}} s}{2} \right) \frac{\mathcal{E} \circ \mathcal{E} \text{ins usl.}}{D} \frac{V_{\text{A}} s}{L^{2}} \\ & \text{Ids} = \left[ \left( V_{\text{A}} s - V_{\text{E}} \right) - \frac{V_{\text{A}} s}{2} \right] \frac{\mathcal{E} \circ \mathcal{E} \text{ins usl.}}{D} \frac{V_{\text{A}} s}{L^{2}} \\ & \text{Ids} = \left[ \left( V_{\text{A}} s - V_{\text{E}} \right) - \frac{V_{\text{A}} s}{2} \right] \frac{\mathcal{E} \circ \mathcal{E} \text{ins usl.}}{D} \frac{V_{\text{A}} s}{L^{2}} \\ & \text{Ids} = \left[ \left( V_{\text{A}} s - V_{\text{E}} \right) \frac{V_{\text{A}} s}{2} - \frac{V_{\text{A}} s}{2} \right] \frac{\mathcal{E} \circ \mathcal{E} \text{ins usl.}}{D} \frac{V_{\text{A}} s}{L^{2}} \\ & \text{Ids} = \left[ \left( V_{\text{A}} s - V_{\text{E}} \right) \frac{V_{\text{A}} s}{2} - \frac{V_{\text{A}} s}{2} \right] \frac{\mathcal{E} \circ \mathcal{E} \text{ins usl.}}{D} \frac{V_{\text{A}} s}{L^{2}} \\ & \text{Ids} = \left[ \left( V_{\text{A}} s - V_{\text{E}} \right) \frac{V_{\text{A}} s}{2} - \frac{V_{\text{A}} s}{2} \right] \\ & \text{Ids} = \frac{\mathcal{E} \text{ins usl.}}{L} \frac{\mathcal{E} \circ \mathcal{E} \text{ins usl.}}{D} \frac{\mathcal{E} \circ \mathcal{E} \text{ins usl.}}{D} \frac{\mathcal{E} \circ \mathcal{E} \text{ins usl.}}{D} \\ & \text{Ids} = \frac{\mathcal{E} \text{ins usl.}}{L} \frac{\mathcal{E} \circ \mathcal{E} \text{ins usl.}}{D} \frac{\mathcal{E} \circ \mathcal{E} \circ \mathcal{E} \text{ins usl.}}{D} \frac{\mathcal{E} \circ \mathcal{E} \text{ins u$$

$$T_{ds} = \frac{c_{g}}{\omega_{L}} \frac{\omega}{\omega} \left[ (v_{gs} - v_{t})v_{ds} - \frac{v_{ds}^{2}}{2} \right]$$

$$T_{ds} = \frac{c_{g}}{L^{2}} \left[ (v_{gs} - v_{t})v_{ds} - \frac{v_{ds}^{2}}{2} \right]$$

$$\omega_{kT} C_{g} = c_{0} \omega_{L}$$

$$T_{ds} = \frac{c_{0}}{\omega} \frac{\omega}{L^{2}} \left[ (v_{gs} - v_{t})v_{ds} - \frac{v_{ds}^{2}}{2} \right]$$

$$Case(a): - Saturation \left[ v_{ds} = v_{gs} - v_{t} \right]$$

$$T_{ds} = \frac{k\omega}{L} \left[ (v_{gs} - v_{t})v_{ds} - \frac{v_{ds}^{2}}{2} \right] \rightarrow (i)$$

$$\Rightarrow Saturation starts at v_{ds} = v_{gs} - v_{t}$$

$$\Rightarrow T_{ds} = \frac{k\omega}{L} \left[ \frac{v_{ds}^{2}}{2} \right]$$

$$T_{ds} = \beta \left[ \frac{v_{gs} - v_{t}}{2} \right]$$

29

While

$$C_{ij} = \frac{k\omega_{ij}}{\lambda} \implies k = \frac{c_{ij}}{\omega_{ij}}$$

$$\Rightarrow Id_{s} = \frac{c_{ij}}{j\omega_{ij}} \frac{\omega_{ij}}{L} \cdot \left(\frac{(\omega_{ij} - v_{ij})^{2}}{\omega_{ij}}\right)$$

$$\boxed{Id_{s}} = \frac{c_{ij}}{L^{2}} \left[\frac{(v_{ij} - v_{ij})^{2}}{\omega_{ij}}\right]$$

$$\boxed{id_{s}} = \frac{c_{oij}}{L^{2}} \left[\frac{(v_{ij} - v_{ij})^{2}}{\omega_{ij}}\right]$$

$$\boxed{Id_{s}} = \frac{c_{oij}}{L} \left[\frac{(v_{ij} - v_{ij})^{2}}{\omega_{ij}}\right]$$

$$\boxed{Trans Conductance} (g_m)$$

$$Trans Conductance (g_m)$$

$$Trans conductance is defined as the relationship between Dutput Current 'Ids' and input. Voltage V_{ijs'}$$

.

$$\therefore g_m = \frac{\delta Id_{s}}{\delta v_{ijs}} |_{vas} = constant$$

$$\frac{\omega_{kT}}{Id_{s}} = \frac{Q_{c}}{\frac{Td_{s}}{1}}$$

$$\frac{Td_{s}}{Id_{s}} = \frac{Q_{c}}{\frac{Td_{s}}{1}}$$

$$\frac{Id_{s}}{\delta Id_{s}} = \frac{\delta c_{ij} mv_{ijs}}{\omega_{ij}}$$

$$\frac{Id_{s}}{\omega_{ij}} = \frac{\delta c_{ij} mv_{ijs}}{\omega_{ij}}$$

$$\frac{\delta Id_{s}}{\omega_{ij}} = \frac{\delta c_{ij} mv_{ijs}}{\omega_{ij}}$$

WKy Re Vgs Re Cg Sugs = Sac · · Jm = SIds Svgs Skicuvas L2 Soc Cg gm = CguVdsWKT Cg = COWL : Jm = CowK HVds 1. L2/ gm = Cowurds Output Conductance [Ids]:-The output Conductance das is defined as the relationship between pulput current Ids and input Voltage Vgs. 16-14-586 = 26-3

$w_0 = u v_{dg}$ Since Vas = Vgs - VE  $U_0 = \mu (v_{g_1} - V_1)$ No mos Inverter-The A-mos inverter is more oftenly use and it Can produce full amount of logic levels. Description :-\* The arrangement of nmos Ri - Depletion mode Inverter consists of depletion mode and enchancement mode transistors. R2 - Enchancement Vin \* Here The gate terminal mode of depletion mode noos is L. Vss Connected to the drain terminal of enchancement mode nmos. of share the best open \* The depletion mode transistor is always on because of the inbuilt channel. Truth Table :-Operation :-Case (1):-Vin 92 Vo 91 when Vin is logic'i' DFF 1 ON 0 When Input is logic 1 the D ON ON transistor B2 turns on and transistor B1 turns on because it is depletion mode

pullup to pulldown ratio of nmas-muester driven by

another nmos inverter:

The arrangement of pullup to pulldown ratio for

one nmos invertes driven by another nmos is

shown as below.

$$V_{DD} = V_{INV} = V_{Vouts}$$

Lok T

I ds for saturation mode

$I ds = \frac{k \omega}{L} \left[ (Vgs - Vt)^2 \right]^2$

for depletion mode vgs=0

$I ds = k \frac{\omega p \omega}{L p \omega} \left[ (\frac{V t d}{\omega}) \right] \longrightarrow (t)$

I ds for enchancement mode,  $Vgs = VinV$

$I ds$  for enchancement mode,  $Vgs = VinV$

$I ds = k \frac{\omega p d}{L p d} \left[ (Vinv - Vt)^2 \right] \longrightarrow (2)$

equating (D and (D,  $O = (D) \ \omega c get$

$\frac{k' \omega p \omega}{L p \omega} \left( -Vt d \right)^2 = \frac{k' \omega p d}{L p d} \left( \frac{Vinv - Vt}{2} \right)^2$

$\frac{1}{r^2 p \omega} \left( -Vt d \right)^2 = \frac{1}{z p d} (Vinv - Vt)^2$

$\frac{1}{r^2 p \omega} \left( -Vt d \right)^2 = \frac{1}{z p d} (Vinv - Vt)^2$

$\frac{2}{2} \frac{P_{U}}{P_{d}} = (0.6 \sqrt{DD})^{2}$   $Vt = 0.2 \sqrt{DD}$ (0.5V00-0.2V00)2 Vinv = 0.5V00 and draw a rate to  $= \left( \frac{0.6 \text{V}_{\text{DD}}}{0.3 \text{V}_{\text{DD}}} \right)^2$ of any of any Zpu = U T stal  $\frac{z_{po}}{z_{pd}} = 4:1$  thous without of the The pullup to pull down ratio of nmos inverter driven by another nmos is 4:1 Pullup to pulldown Jutio of nimos driven by another nmos with one or more pass transistors. The arrangement of pullup to pulldown ratio for nons driven by another nons with one or more pass transistors is depicted as below. VDD VDD VDD VDD VEP VOL VPD \* when the output of invertex 1 is passed through series of pass Ti transistors. then full logic levels are not obtain due to threshold voltage of pass transistors.ie., Vinuz=Voo-Vy.

www.Jntufastupdates.com

www.Jntufastupdates.com

$\frac{d_{s_1}}{V_{d_{s_1}}} = \frac{k}{Z_{pd_1}} \left( V_{0,D} - V_{L} \right)$  $\frac{1}{P_{I}} = \frac{k}{\epsilon P_{A_{I}}} \left( V_{pp} \cdot V_{t} \right)$  $R_1 = \frac{7 p d_1}{K(v_{bp} - v_t)}$ VO1 = J, R,  $V_{01} = \frac{18}{2} \left(\frac{-V_{td}}{2}\right)^2 \frac{7}{2} \frac{2pd1}{k(V_{DD} - V_{t})}$  $V_{01} = \frac{ZPa1}{ZPU1} \frac{(-Vta)^2}{Q(VDD-Vt)}$ For inverter 2 For saturation mode, Ids. con be seen by  $I_{ds} = \frac{k\omega}{L} \left( \frac{V_{gs} - VL}{L} \right)^2$ For depletion mode, vgs=0 Ids\_ = Kuopuz (-Vtd)2  $\frac{T_{a}}{Z_{p}} = \frac{k}{Z_{p}} \left(-\frac{VLd}{2}\right)^{2}$ Ids in non-saturation can be given by Ids = KLO [[Vgs-VE]Vds - Vds] pairalpa

For enhancement mode,

$$vgs = Vop - Vtp$$

$$Tds_{2} = \frac{k\omega pd_{2}}{LRd_{2}} \left[ (vgs - vt) Vds_{2} - \frac{vds_{2}^{2}}{2} \right]$$

$$Tds_{2} = \frac{k}{Zpd_{2}} \left[ (vgs - vt) - \frac{Vds}{2} \right]$$

$$reglecting$$

$$\frac{1}{P_{2}} = \frac{k}{Zpd_{2}} \left[ vgs - vt \right]$$

$$\frac{1}{P_{2}} = \frac{k}{Zpd_{2}} \left[ vgs - vt \right]$$

$$\frac{1}{R_{2}} = \frac{-k}{Zpd_{2}} \left[ (vop - Vtp - vt) \right]$$

$$\frac{1}{R_{2}} = \frac{-k}{Zpd_{2}} \left[ (vop - Vtp - vt) \right]$$

$$\frac{1}{R_{2}} = \frac{-k}{Zpd_{2}} \left[ (vop - Vtp - vt) \right]$$

$$Vo_{2} = TaR_{2}$$

$$= \frac{kV}{Zpv_{2}} \left( \frac{-Vtd}{2} \right)^{2} \frac{7Pd_{2}}{V(vop - Vtp - vt)}$$

$$\frac{1}{Vo_{2}} = \frac{7Pd_{2}}{Zpv_{2}} \left( \frac{-Vtd}{2} \right)^{2} \frac{V(vop - Vtp - vt)}{V(vop - vtp - vt)}$$

$$\frac{1}{Vo_{1}} = \frac{ZPd_{1}}{Zpv_{1}} \left( \frac{-Vtd}{2} \right)^{2} \frac{V}{V(vop - vtp - vt)}$$

$$\frac{1}{Zpv_{1}} \frac{1}{a} \left( \frac{-Vtd}{2} \right)^{2} \frac{V}{a} \left( \frac{-Vtd}{2} \right)^{2} \frac{V}{a} \left( \frac{-Vtd}{2} \right)^{2}}{Zpv_{1}} \frac{1}{a} \left( \frac{-Vtd}{2} \right)^{2} \frac{Vtp - vt}{a}$$

$$\frac{2p_{H1}}{2p_{V1}(V_{DD}-V_{L})} = \frac{2p_{D2}}{2p_{V2}(V_{DD}-V_{LP}-V_{L})}$$

$$\frac{2p_{D2}}{2p_{V2}} = \frac{2p_{H1}(v_{DD}-V_{L}-V_{L})}{2p_{H2}}$$

$$\frac{2p_{V2}}{2p_{H2}} = \frac{2p_{V1}(v_{DD}-v_{L})}{2p_{H1}(v_{DD}-v_{L}-V_{L})}$$

$$\frac{2p_{V2}}{2p_{H2}} = \frac{4}{1} \times \frac{V_{DD}-0.2V_{DD}}{V_{DD}-0.2V_{DD}}$$

$$V_{LP} = 0.3v_{DD}$$

$$\frac{2p_{V2}}{2p_{H2}} = \frac{4}{1} \times \frac{v_{DD}-0.2V_{DD}}{v_{DD}-0.2V_{DD}}$$

$$= \frac{4}{1} \times \frac{v_{B}}{v_{D}} \frac{v_{PD}}{v_{DD}}$$

$$= \frac{2p_{V2}}{1} \times \frac{s_{B}}{v_{D}}$$

$$= \frac{2p_{V2}}{2p_{V2}} \approx \frac{s_{B}}{1}$$

$$= \frac{2p_{V2}}{2p_{V2}} \approx \frac{s_{B}}{1}$$

$$\therefore \text{ The pullup to pulldown statio of nmos driven by another nmos with one or mose pass transitions by another nmos with one or mose pass transitions is s:1$$

$$= \frac{1}{v_{D}} \frac{v_{D}}{v_{D}} = \frac{1}{v_{D}} \frac{v_{D}}{v_{D}} = \frac{1}{v_{D}} \frac{v_{D}}{v_{D}} + \frac{1}{v_{D}} \frac{v_{D}}{v_{D}} = \frac{1}{v_{D}} \frac{v_{D}}{v_{D}} + \frac{1}{v_{D}} \frac{v_{$$

www.Jntufastupdates.com

www.Jntufastupdates.com

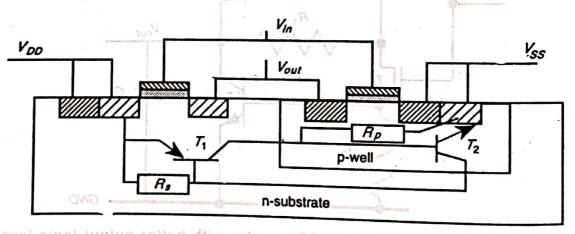

The Transistors T5, T6 will get - furn ON when Thand Tz Despectively being turn off. · Latch up in CHOS -\* Latch of is a inherent problem in CHOS, that provide a low impedance path between vob and Vss. \* latch up may arise due to noise, switch on and OFF or by Incident radiation. \* The latch up mechanism can be better under -stood with the following arrangement. thread signal as the 4 V q vin P pite 0 Vpp 9 Vo VSS Alle Shines 11/2 TID Mi al Y pnt n q pt nt RW Rs 1.11 m P-Sub latch up effecting n-well substrate

\* in the above figure, if sufficient substrate current flows for ap, then ap will turn on fift draws some current through Rs.

\* If it is enough to drive an then it will also turn on.

tence a short circuit path blue Vop and Uss is obtained and it is called as latch up problem.

www.Jntufastupdates.com

\* Oxidation: - Processing steps for fabrication of Ici. Silicon is one of mostly used oxidised moterial and which may also acts as good masking element.

\* To perform oxidation process let us consider a furnace with silicon and rise the temperature.

\* Oxidation is two types 1) Dray orridation: Hese the silicon is steacting with 02 to Form 3i02.

Si + 02 → Si02

2) Lot orridation: Silicon steacts with H20 to form Si02.

Si + 2H<sub>2</sub>O  $\longrightarrow$  SiO<sub>2</sub> + DH<sub>2</sub> We Have O<sub>2</sub>, H<sub>2</sub>O are called Dridonts that are up to Oridise Silicon. \* <u>ion implantation:</u>-

ion implantation process is use to diffuse the dopands into a specified motestial (or) Substrate.

\* Here the dopond is to be diffuse into a substrate material with a sufficient energy.

\* By the strength of the dopand it penterates through the substrate and may cause some effect on lattice atom.

Nuckear stoping: - when the dopand is injected into the Substrate, depending upon the strength the dopand

may change the position of lattice atom and may damage the lattice atom. If the strength is further more increase. Hence it is called Nuclear stoping. electronic \* During ion implantation process, if the dopands

change the position of the lattice atom and it is Shows no damage of latticeator thence it is called electronic stoping.

slight

\* photolithography (or) lithography:-a project Floot is depands, into photolithography is used to diffuse dopands. into Substrate in a selected position through masking element.

i.e., Lithography (or) photolithography is the process of transfering geometrical patterns from mosking element to silicon.

\* In olden days, we don't have photolithography technology then a mask of Suitable pattern is transfer into Silicon using a litho (stone).

\* Metalization -

Metalization is the process that is use to expect terminals from the device. These terminals are used to have contact to the outside world. that is means to measure output (throughput)

Metalization ohmic contacts (AP) Normal silicides (poly + silicon) \* Encapsulation:-Encapsulation is the process that is use after manufacturing of the device. Encopsulation provides protection to the Whole body (01) package. the of st of Whener Manual a tear winny will a st Straite | testation of provide

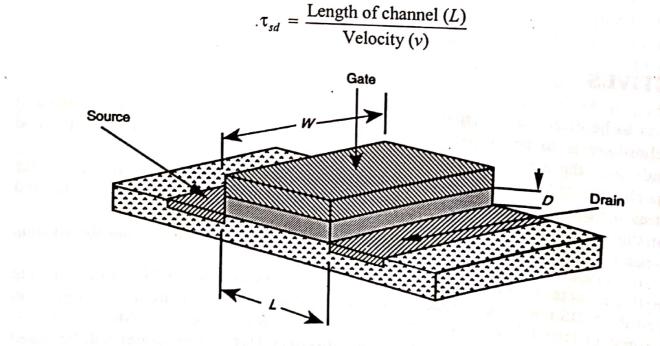

# 2.1 DRAIN-TO-SOURCE CURRENT Ids versus VOLTAGE Vds RELATIONSHIPS

The whole concept of the MOS transistor evolves from the use of a voltage on the gate to induce a charge in the channel between source and drain, which may then be caused to move from source to drain under the influence of an electric field created by voltage  $V_{ds}$  applied between drain and source. Since the charge induced is dependent on the gate to source voltage  $V_{gs}$ , then  $I_{ds}$  is dependent on both  $V_{gs}$  and  $V_{ds}$ . Consider a structure, as in Figure 2.1, in which electrons will flow source to drain:

$$I_{ds} = -I_{sd} = \frac{\text{Charge induced in channel } (Q_c)}{\text{Electron transit time } (\tau)}$$

(2.1)

First, transit time:

$v = \mu E_{ds}$

but velocity

where

$\mu$  = electron or hole mobility (surface)  $E_{ds}$  = electric field (drain to source) Now

$$E_{ds} = \frac{V_{ds}}{L}$$

so that

Thus

$v = \frac{\mu V_{ds}}{L}$

$\tau_{sd} = \frac{L^2}{\mu V_{to}}$

(2.2)

Typical values of  $\mu$  at room temperature are:

$\mu_n = 650 \text{ cm}^2/\text{V} \text{ sec (surface)}$  $\mu_p = 240 \text{ cm}^2/\text{V} \text{ sec (surface)}$

# 2.1.1 The Non-saturated Region

Charge induced in channel due to gate voltage is due to the voltage difference between the gate and the channel,  $V_{gs}$  (assuming substrate connected to source). Now note that the voltage along the channel varies linearly with distance X from the source due to the IR drop in the channel (see Figure 1.5) and assuming that the device is not saturated then the average value is  $V_{ds}/2$ . Furthermore, the effective gate voltage  $V_g = V_{gs} - V_t$  where  $V_t$  is the threshold voltage needed to invert the charge under the gate and establish the channel.

Note that the charge/unit area =  $E_g \varepsilon_{ins} \varepsilon_0$ . Thus induced charge

$$Q_c = E_g \varepsilon_{ins} \varepsilon_0 WL$$

where

$E_g$  = average electric field gate to channel

$\varepsilon_{ins}$  = relative permittivity of insulation between gate and channel

$\varepsilon_0$  = permittivity of free space

20

(*Note:*  $\epsilon_0 = 8.85 \times 10^{-14} \text{F cm}^{-1}$ ;  $\epsilon_{ins} \neq 4.0$  for silicon dioxide)

Now

$$E_g = \frac{\left( (V_{gs} - V_l) - \frac{V_{ds}}{2} \right)}{D}$$

where D = oxide thickness.

Thus

$$Q_{c} = \frac{WL\varepsilon_{ins}\varepsilon_{0}}{D} \left( (V_{gs} - V_{t}) - \frac{V_{ds}}{2} \right)$$

(2.3)

Now, combining equations (2.2) and (2.3) in equation (2.1), we have

$$I_{ds} = \frac{\varepsilon_{ins}\varepsilon_{0}\mu}{D}\frac{W}{L}\left((V_{gs} - V_{t}) - \frac{V_{ds}}{2}\right)V_{ds}$$

or

$$I_{ds} = K \frac{W}{L} \left( (V_{gs} - V_{l}) V_{ds} - \frac{V_{ds}^{2}}{2} \right)$$

in the non-saturated or resistive region where  $V_{ds} < V_{gs} - V_l$  and

$K = \frac{\varepsilon_{ins}\varepsilon_0\mu}{D}$

The factor W/L is, of course, contributed by the geometry and it is common practice to write

$$\beta = K \frac{W}{L}$$

so that

$$I_{ds} = \beta \left( (V_{gs} - V_t) V_{ds} - \frac{V_{ds}^2}{2} \right)$$

(2.4a)

(2.4)

which is an alternative form of equation (2.4). Noting that gate/channel capacitance

$$C_g = \frac{\varepsilon_{lns}\varepsilon_0 WL}{D}$$

(parallel plate)

we also have

$$K = \frac{C_g \mu}{WL}$$

so that

3

$$I_{ds} = \frac{C_g \mu}{L^2} \left( (V_{gs} - V_i) V_{ds} - \frac{V_{ds}^2}{2} \right)$$

(2.4b)

which is a further alternative form of equation (2.4).

Sometimes it is convenient to use gate capacitance per unit area  $C_0$  (which is often denoted  $C_{ox}$ ) rather than  $C_g$  in this and other expressions. Noting that

$$C_g = C_0 WL$$

we may also write

$$I_{ds} = C_0 \mu \frac{W}{L} \left( (V_{gs} - V_t) V_{ds} - \frac{V_{ds}^2}{2} \right)$$

(2.4c)

## 2.1.2 The Saturated Region

Saturation begins when  $V_{ds} = V_{gs} - V$ , since at this point the *IR* drop in the channel equals the effective gate to channel voltage at the drain and we may assume that the current remains fairly constant as  $V_{ds}$  increases further. Thus

$$I_{ds} = K \frac{W}{L} \frac{(V_{gs} - V_t)^2}{2}$$

(2.5)

or, we may write

$$I_{ds} = \frac{\beta}{2} \left( V_{gs} - V_t \right)^2$$

(2.5a)

OL

$$I_{ds} = \frac{C_g \mu}{2L^2} \left( V_{gs} - V_t \right)^2$$

(2.5b)

We may also write

$$I_{ds} = C_0 \mu \frac{W}{2L} \left( V_{gs} - V_t \right)^2 \quad \text{minor electric product of the }$$

(2.5c)

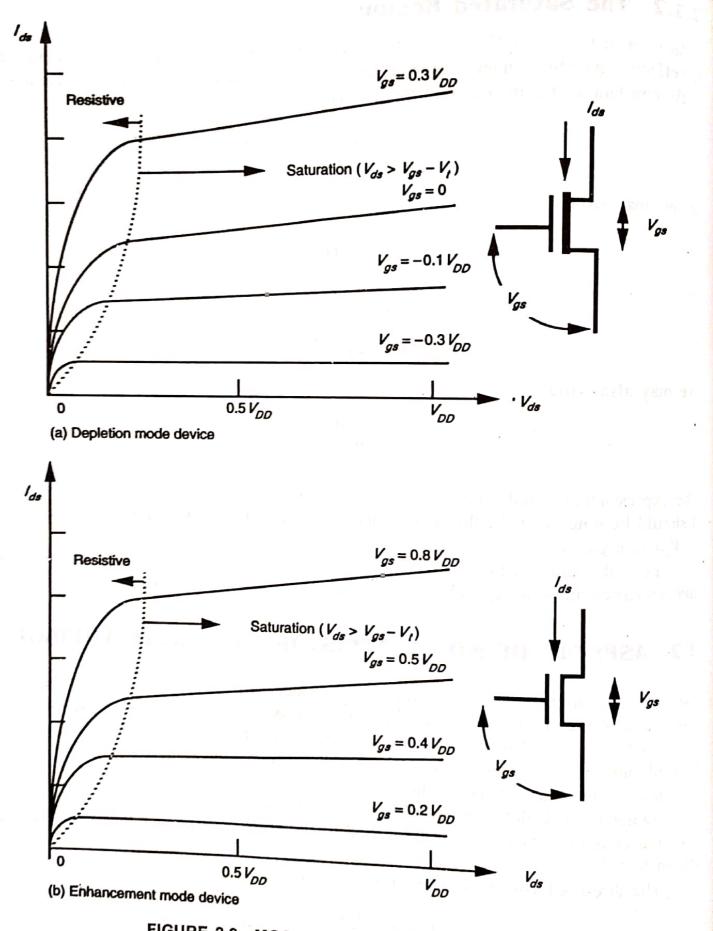

The expressions derived for  $I_{ds}$  hold for both enhancement and depletion mode devices, but it should be noted that the threshold voltage for the nMOS depletion mode device (denoted as  $V_{td}$ ) is negative.

Typical characteristics for nMOS transistors are given in Figure 2.2. pMOS transistor characteristics are similar, with suitable reversal of polarity.

# 2.2 ASPECTS OF MOS TRANSISTOR THRESHOLD VOLTAGE $V_t$

The gate structure of a MOS transistor consists, electrically, of charges stored in the dielectric layers and in the surface to surface interfaces as well as in the substrate itself.

Switching an enhancement mode MOS transistor from the off to the on state consists in applying sufficient gate voltage to neutralize these charges and enable the underlying silicon to undergo an inversion due to the electric field from the gate.

Switching a depletion mode nMOS transistor from the on to the off state consists in applying enough voltage to the gate to add to the stored charge and invert the 'n' implant region to 'p'.

The threshold voltage  $V_t$  may be expressed as:

$$V_{l} = \phi_{ms} \frac{Q_{B} - Q_{SS}}{C_{0}} + 2\phi_{fN}$$

(2.6)

where

$Q_B$  = the charge per unit area in the depletion layer beneath the oxide  $Q_{SS}$  = charge density at Si:SiO<sub>2</sub> interface

Scanned by CamScanner

$C_0$  = capacitance per unit gate area

$\phi_{ms}$  = work function difference between gate and Si

$\phi_{IN}$  = Fermi level potential between inverted surface and bulk Si.

Now, for polysilicon gate and silicon substrate, the value of  $\phi_{ms}$  is negative but negligible, and the magnitude and sign of  $V_t$  are thus determined by the balance between the remaining  $-Q_{ss}$

negative term  $\frac{-Q_{SS}}{C_0}$  and the other two terms, both of which are positive. To evaluate  $V_t$ , each term is determined as follows:

$$Q_B = \sqrt{2\varepsilon_0 \varepsilon_{Si} q N (2\phi_{fN} + V_{SB})} \text{ coulomb/m}^2$$

$$\phi_{fN} = \frac{kT}{q} \ln \frac{N}{n_i} \text{ volts}$$

$Q_{SS} = (1.5 \text{ to } 8) \times 10^{-8} \text{ coulomb/m}^2$

depending on crystal orientation, and where

$V_{SB}$  = substrate bias voltage (negative w.r.t. source for nMOS, positive for pMOS)  $q = 1.6 \times 10^{-19}$  coulomb

N = impurity concentration in the substrate ( $N_A$  or  $N_D$  as appropriate)

- $\varepsilon_{si}$  = relative permittivity of silicon  $\Rightarrow$  11.7

- $n_i$  = intrinsic electron concentration (1.6 × 10<sup>10</sup>/cm<sup>3</sup> at 300°K)

k = Boltzmann's constant =  $1.4 \times 10^{-23}$  joule/°K

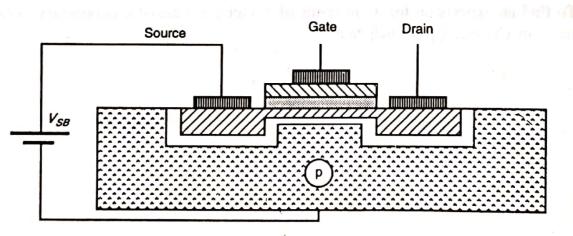

The *body effects* may also be taken into account since the substrate may be biased with respect to the source, as shown in Figure 2.3.

FIGURE 2.3 Body effect (nMOS device shown).

Increasing  $V_{SB}$  causes the channel to be depleted of charge carriers and thus the threshold voltage is raised.

Change in  $V_t$  is given by  $\Delta V_t \neq \gamma (V_{SB})^{1/2}$  where  $\gamma$  is a constant which depends on substrate doping so that the more lightly doped the substrate, the smaller will be the body effect.

Alternatively, we may write

$$V_{t} = V_{t}(0) + \left(\frac{D}{\varepsilon_{ins}\varepsilon_{0}}\right) \sqrt{2\varepsilon_{0}\varepsilon_{Si}QN} \cdot (V_{SB})^{1/2}$$

where  $V_t(0)$  is the threshold voltage for  $V_{SB} = 0$ . To establish the magnitude of such effects, typical figures for  $V_t$  are as follows:

For nMOS enhancement mode transistors:

$$V_{SB} = 0 \text{ V}; V_{t} = 0.2V_{DD} (= +1 \text{ V for } V_{DD} = +5 \text{ V}) \begin{cases} \text{Similar but} \\ \text{negative values} \end{cases}$$

For nMOS depletion mode transistors:

$$V_{SB} = 0 \text{ V}; V_{td} = -0.7V_{DD} (= -3.5 \text{ V for } V_{DD} = +5 \text{ V})$$

$V_{SB} = 5 \text{ V}; V_{td} = -0.6V_{DD} (= -3.0 \text{ V for } V_{DD} = +5 \text{ V})$

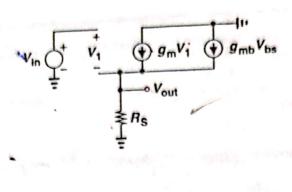

#### MOS TRANSISTOR TRANSCONDUCTANCE $g_m$ AND OUTPUT 2.3 CONDUCTANCE $g_{ds}$

Transconductance expresses the relationship between output current  $I_{ds}$  and the input voltage  $V_{gs}$  and is defined as

$$g_m = \frac{\delta I_{ds}}{\delta V_{gs}} | V_{ds} = \text{constant}$$

To find an expression for  $g_m$  in terms of circuit and transistor parameters, consider that the charge in channel  $Q_c$  is such that

$$\frac{Q_c}{I_{ds}} = \tau$$

where  $\tau$  is transit time. Thus change in current

$$\delta I_{ds} = \frac{\delta Q_c}{\tau_{ds}}$$

Now

$$\tau_{ds} = \frac{L^2}{\mu V_{ds}}$$

(from 2.2)

Thus

$$\delta I_{ds} = \frac{\delta Q_c V_{ds} \mu}{L^2}$$

www.Jntufastupdates.com

Scanned by CamScanner

(2.7)

-3:5V.10 -3.010

but change in charge

so that

140\*\*

$$g_m = \frac{\delta I_{ds}}{\delta V_{gs}} = \frac{C_g \mu V_{ds}}{L^2}$$

$V_{ds} = V_{gs} - V_t$  as sevel more seven

$g_m = \frac{C_g \mu}{I^2} \left( V_{gs} - V_t \right)$

$\delta I_{ds} = \frac{C_g \delta V_{gs} \mu V_{ds}}{I^2} O^{-6}$

In saturation

Compare this with the typical bulk mobilities

and substituting for

$$C_g = \frac{\varepsilon_{ins}\varepsilon_0 WL}{D}$$

()

$$g_m = \frac{\mu \varepsilon_{ins} \varepsilon_0}{D} \frac{W}{L} (V_{gs} - V_t)$$

(2.7a)

Alternatively,

$g_m = \beta (V_{gs} - V_l)$

It is possible to increase the  $g_m$  of a MOS device by increasing its width. However, this will also increase the input capacitance and area occupied.

A reduction in the channel length results in an increase in  $\omega_0$  owing to the higher  $g_m$ . However, the gain of the MOS device decreases owing to the strong degradation of the output resistance =  $1/g_{ds}$ .

The output conductance  $g_{ds}$  can be expressed by

$$g_{ds} = \frac{\delta I_{ds}}{\delta V_{gs}} = \lambda . I_{ds} \alpha \left(\frac{1}{L}\right)^2$$

Here the strong dependence on the channel length is demonstrated as

$$\lambda \alpha \left(\frac{1}{L}\right)$$

and  $I_{ds} \alpha \left(\frac{1}{L}\right)$

for the MOS device.

www.Jntufastupdates.com

Scanned by CamScanner

# 2.4 MOS TRANSISTOR FIGURE OF MERIT $\omega_0$

An indication of frequency response may be obtained from the parameter  $\omega_0$  where

$$\omega_0 = \frac{g_m}{C_g} = \frac{\mu}{L^2} \left( V_{gs} - V_t \right) \left( = \frac{1}{\tau_{sd}} \right)$$

(2.8)

This shows that switching speed depends on gate voltage above threshold and on carrier mobility and inversely as the square of channel length. A fast circuit requires that  $g_m$  be as high as possible.

Electron mobility on a (100) oriented n-type inversion layer surface  $(\mu_n)$  is larger than that on a (111) oriented surface, and is in fact about three times as large as hole mobility on a (111) oriented p-type inversion layer. Surface mobility is also dependent on the effective gate voltage  $(V_{gs} - V_l)$ .

For faster nMOS circuits, then, one would choose a (100) oriented p-type substrate in which the inversion layer will have a surface carrier mobility  $\mu_n \neq 650 \text{ cm}^2/\text{V}$  sec at room temperature.

Compare this with the typical bulk mobilities

$$\mu_n = 1250 \text{ cm}^2/\text{V} \text{ sec}$$

$\mu_n = 480 \text{ cm}^2/\text{V} \text{ sec}$

from which it will be seen that  $\frac{\mu_s}{\mu} = 0.5$  (where  $\mu_s = \text{surface mobility and } \mu = \text{bulk mobility}$ ).

## 2.5 THE PASS TRANSISTOR

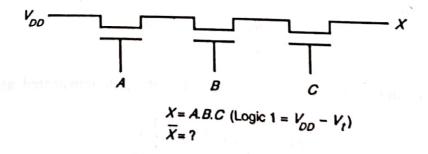

Unlike bipolar transistors, the isolated nature of the gate allows MOS transistors to be used as switches in series with lines carrying logic levels in a way that is similar to the use of relay contacts. This application of the MOS device is called the *pass transistor* and switching logic arrays can be formed—for example, an *And* array as in Figure 2.4.

Note: Means must exist so that X assumes ground potential when  $A + B + C = Q_{-}$ FIGURE 2.4 Pass transistor And gate.

9

# 2.6 THE nMOS INVERTER

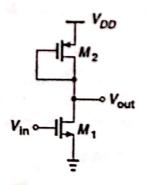

A basic requirement for producing a complete range of logic circuits is the inverter. This is needed for restoring logic levels, for *Nand* and *Nor* gates, and for sequential and memory circuits of various forms. In the treatment of the inverter used in this section, the authors wish to acknowledge the influence of material previously published by Mead and Conway.

The basic inverter circuit requires a transistor with source connected to ground and a load resistor of some sort connected from the drain to the positive supply rail  $V_{DD}$ . The output is taken from the drain and the input applied between gate and ground.

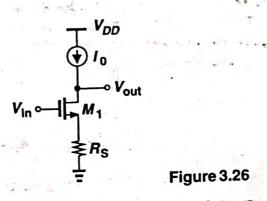

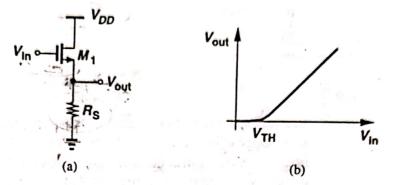

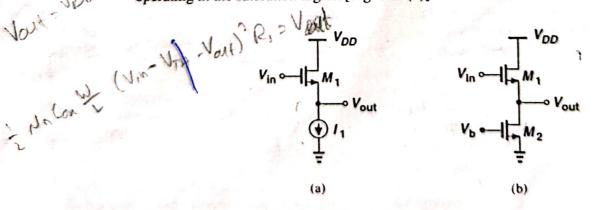

Resistors are not conveniently produced on the silicon substrate; even modest values occupy excessively large areas so that some other form of load resistance is required. A convenient way to solve this problem is to use a depletion mode transistor as the load, as shown in Figure 2.5.

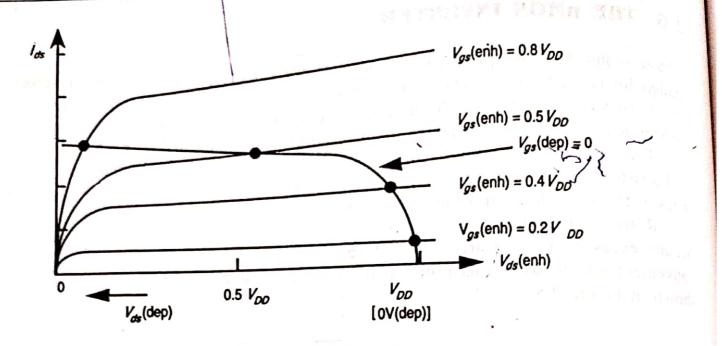

FIGURE 2.5 nMOS inverter.

Now:

- With no current drawn from the output, the currents  $I_{ds}$  for both transistors must be equal.

- For the depletion mode transistor, the gate is connected to the source so it is always on and only the characteristic curve  $V_{gs} = 0$  is relevant.

- In this configuration the depletion mode device is called the pull-up (p.u.) and the enhancement mode device the pull-down (p.d.) transistor.

- To obtain the inverter transfer characteristic we superimpose the  $V_{gs} = 0$  depletion mode characteristic curve on the family of curves for the enhancement mode device, noting that maximum voltage across the enhancement mode device corresponds to minimum voltage across the depletion mode transistor.

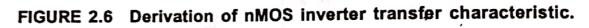

- The points of intersection of the curves as in Figure 2.6 give points on the transfer characteristic, which is of the form shown in Figure 2.7.

- Note that as  $V_{in}(=V_{gs}$  p.d. transistor) exceeds the p.d. threshold voltage current begins to flow. The output voltage  $V_{out}$  thus decreases and the subsequent increases in  $V_{in}$  will cause the p.d. transistor to come out of saturation and become resistive. Note that the p.u. transistor is initially resistive as the p.d. turns on.

$V_{ds}(enh) = V_{DD} - V_{ds}(dep) = V_{out}$  $V_{gs}(enh) = V_{in} \dots$  intersection points give transfer characteristic

nMOS inverter transfer characteristic.

• During transition, the slope of the transfer characteristic determines the gain:

$$Gain = \frac{\delta V_{out}}{\delta V_{in}}$$

www.Jntufastupdates.com

• The point at which  $V_{out} = V_{in}$  is denoted as  $V_{inv}$  and it will be noted that the transfer characteristics and  $V_{inv}$  can be shifted by variation of the ratio of pull-up to pull-down resistances (denoted  $Z_{p.u.}/Z_{p.d.}$  where Z is determined by the length to width ratio of the transistor in question).

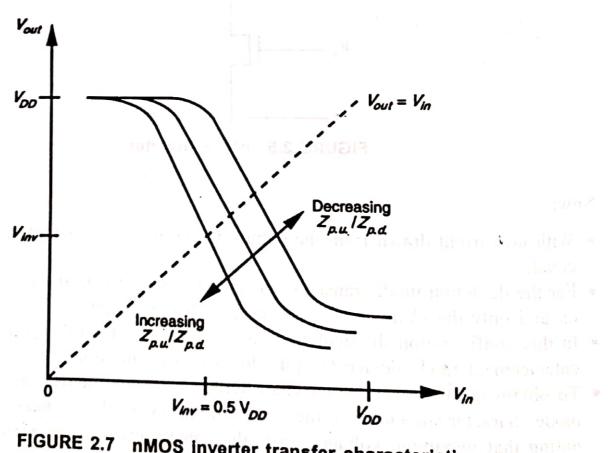

# DETERMINATION OF PULL-UP TO PULL-DOWN RATIO $(Z_{p.u}/Z_{p.d.})$ FOR AN nMOS INVERTER DRIVEN BY ANOTHER nMOS INVERTER

Consider the arrangement in Figure 2.8 in which an inverter is driven from the output of another similar inverter. Consider the depletion mode transistor for which  $V_{gs} = 0$  under all conditions, and further assume that in order to cascade inverters without degradation of levels we are aiming to meet the requirement

FIGURE 2.8 nMOS inverter driven directly by another inverter.

For equal margins around the inverter threshold, we set  $V_{inv} = 0.5V_{DD}$ . At this point both transistors are in saturation and

$$I_{ds} = K \frac{W}{L} \frac{\left(V_{gs} - V_{l}\right)^{2}}{2}$$

In the depletion mode

$$I_{ds} = K \frac{W_{p.u.}}{L_{p.u.}} \frac{(-V_{td})^2}{2} \text{ since } V_{gs} = 0$$

and in the enhancement mode

$$I_{ds} = K \frac{W_{p.d.}}{L_{p.d.}} \frac{(V_{inv} - V_t)^2}{2} \text{ since } V_{gs} = V_{inv}$$

Equating (since currents are the same) we have

$$\frac{W_{p.d.}}{L_{p.d.}} \left( V_{inv} - V_{t} \right)^{2} = \frac{W_{p.u.}}{L_{p.u.}} \left( -V_{td} \right)^{2}$$

D

where  $W_{p.d.}$ ,  $L_{p.d.}$ ,  $W_{p.u.}$ , and  $L_{p.u.}$  are the widths and lengths of the pull-down and pull-up transistors respectively.

Now write

$$Z_{p.d.} = \frac{L_{p.d.}}{W_{p.d.}}; Z_{p.u.} = \frac{L_{p.u.}}{W_{p.u.}}$$

we have

$$\frac{1}{Z_{p.d.}} (V_{inv} - V_t)^2 = \frac{1}{Z_{p.u.}} (-V_{td})^2$$

whence

$$V_{inv} = V_t - \frac{V_{td}}{\sqrt{Z_{p.u.}/Z_{p.d.}}}$$

(2.9)

Now we can substitute typical values as follows:

$V_t = 0.2 V_{DD}; V_{td} = -0.6 V_{DD}$  $V_{inv} = 0.5 V_{DD}$  (for equal margins)

thus, from equation (2.9)

$$0.5 = 0.2 + \frac{0.6}{\sqrt{Z_{p,u}/Z_{p,d}}}$$

whence

$$\sqrt{Z_{p.u.}/Z_{p.d.}} = 2$$

and thus

$$Z_{p.u.}/Z_{p.d.} = 4/1$$

for an inverter directly driven by an inverter.

# 2.8 PULL-UP TO PULL-DOWN RATIO FOR AN MMOS INVERTER DRIVEN THROUGH ONE OR MORE PASS TRANSISTORS

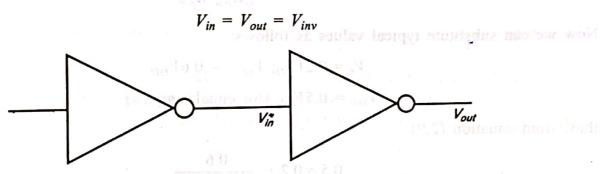

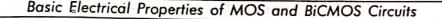

Now consider the arrangement of Figure 2.9 in which the input to inverter 2 comes from the output of inverter 1 but passes through one or more nMOS transistors used as switches in series (called *pass transistors*).

We are concerned that connection of pass transistors in series will degrade the logic 1 level (into inverter 2 so that the output will not be a proper logic 0 level. The critical condition is when point A is at 0 volts and B is thus at  $V_{DD}$ , but the voltage into inverter 2 at point C is now reduced from  $V_{DD}$  by the threshold voltage of the series pass transistor. With all pass transistor gates connected to  $V_{DD}$  (as shown in Figure 2.8), there is a loss of

38

\_

FIGURE 2.9 Pull-up to pull-down ratios for inverting logic coupled by pass transistors.

$V_{tp}$ , however many are connected in series, since no static current flows through them and there can be no voltage drop in the channels. Therefore, the input voltage to inverter 2 is

$$V_{in2} = V_{DD} - V_{tp}$$

where

$V_{tp}$  = threshold voltage for a pass transistor.

We must now ensure that for this input voltage we get out the same voltage as would be the case for inverter 1 driven with input =  $V_{DD}$ .

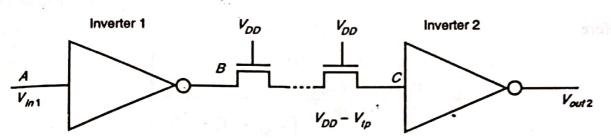

Consider inverter 1 (Figure 2.10(a)) with input =  $V_{DD}$ . If the input is at  $V_{DD}$ , then the p.d. transistor  $T_2$  is conducting but with a low voltage across it; therefore, it is in its resistive region represented by  $R_1$  in Figure 2.10. Meanwhile, the p.u. transistor  $T_1$  is in saturation and is represented as a current source.

FIGURE 2.10 Equivalent circuits of inverters 1 and 2.

For the p.d. transistor

$$I_{ds} = K \frac{W_{p.d.1}}{L_{p.d.1}} \left( (V_{DD} - V_t) V_{ds1} - \frac{V_{ds1}^2}{2} \right)$$

(from 2.4)

of 18,2 i

Therefore

$$R_{1} = \frac{V_{ds1}}{I_{ds}} = \frac{1}{K} \frac{L_{p.d.1}}{W_{p.d.1}} \left( \frac{1}{V_{DD} - V_{t} - \frac{V_{ds1}}{2}} \right)$$

Note that  $V_{ds1}$  is small and  $V_{ds1}/2$  may be ignored. Thus

$$R_1 \doteq \frac{1}{K} Z_{p.d.1} \left( \frac{1}{V_{DD} - V_t} \right)$$

Now, for depletion mode p.u. in saturation with  $V_{gs} = 0$

$$I_1 = I_{ds} = K \frac{W_{p.u.1}}{L_{p.u.1}} \frac{(-V_{td})^2}{2}$$

(from 2.5)

The product

$$I_1 R_1 = V_{out \ 1}$$

Thus

$$V_{out1} = I_1 R_1 = \frac{Z_{p.d.1}}{Z_{p.u.1}} \left(\frac{1}{V_{DD} - V_t}\right) \frac{(V_{td})^2}{2}$$

Consider inverter 2 (Figure 2.10(b)) when input =  $V_{DD} - V_{tp}$ . As for inverter 1

$$R_{2} \neq \frac{1}{K} Z_{p.d.2} \frac{1}{((V_{DD} - V_{tp}) - V_{t})}$$

$$I_{2} = K \frac{1}{Z_{p.u.2}} \frac{(-V_{td})^{2}}{2}$$

whence

$$V_{out\,2} = I_2 R_2 = \frac{Z_{p.d.2}}{Z_{p.u.2}} \left( \frac{1}{V_{DD} - V_{tp} - V_t} \right) \frac{(-V_{td})^2}{2}$$

If inverter 2 is to have the same output voltage under these conditions then  $V_{out 1} = V_{out 2}$ . That is

$$I_1 R_1 = I_2 R_2$$

Therefore

$$\frac{Z_{p.u.2}}{Z_{p.d.2}} = \frac{Z_{p.u.1}}{Z_{p.d.1}} \frac{(V_{DD} - V_t)}{(V_{DD} - V_{tp} - V_t)}$$

www.Jntufastupdates.com

#### Scanned by CamScanner

# Taking typical values

$V_t = 0.2V_{DD}$   $V_{tp} = 0.3V_{DD}^*$   $Z_{THZ} = Z_{THZ} = 0.8$

$$\frac{Z_{p.u.2}}{Z_{p.d.2}} = \frac{Z_{p.u.1}}{Z_{p.d.1}} \frac{0.8}{0.5}$$

Therefore

$$\frac{Z_{p.u.2}}{Z_{p.d.2}} \div 2 \ \frac{Z_{p.u.1}}{Z_{p.d.1}} = \frac{8}{1}$$

Summarizing for an nMOS inverter:

- An inverter driven directly from the output of another should have a  $Z_{p.u}/Z_{p.d.}$  ratio of  $\geq 4/1$ .

- An inverter driven through one or more pass transistors should have a  $Z_{p.u.}/Z_{p.d.}$  ratio of  $\geq 8/1$ .

Note: It is the driven, not the driver, whose ratio is affected/

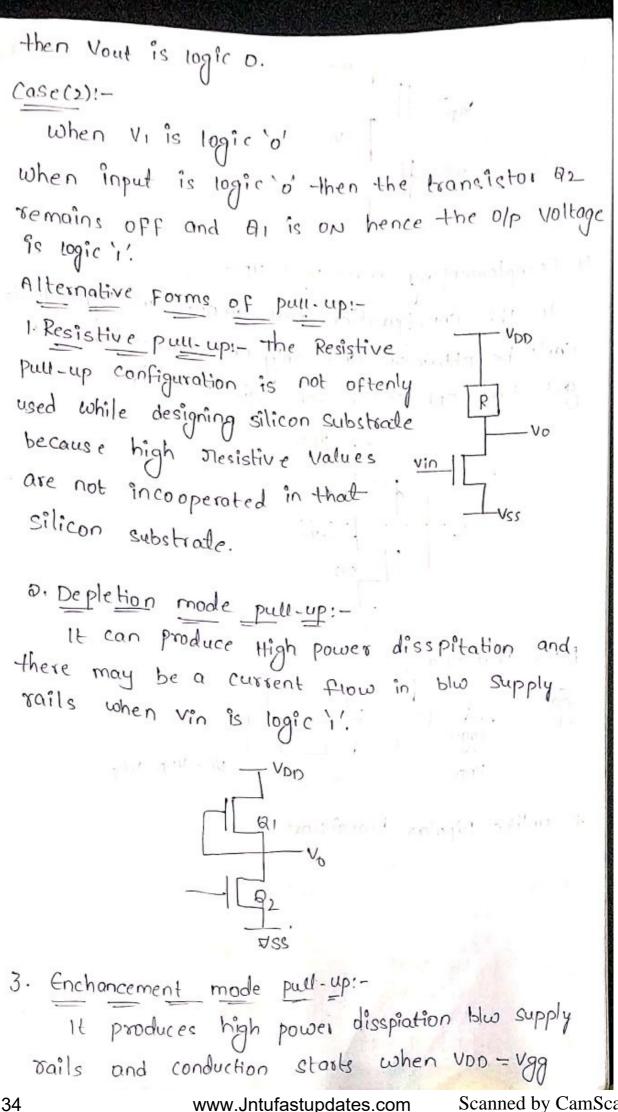

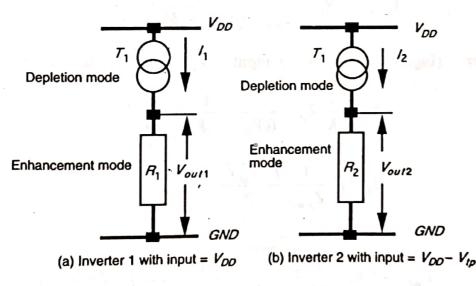

# 2.9 ALTERNATIVE FORMS OF PULL-UP detailed sold

Up to now we have assumed that the inverter circuit has a depletion mode pull-up transistor as its load. There are, however, at least four possible arrangements:

1. Load resistance  $R_L$  (Figure 2.11). This arrangement is not often used because of the large space requirements of resistors produced in a silicon substrate.

www.Jntufastupdates.com

Scanned by CamScanner

# Basic VLSI Design

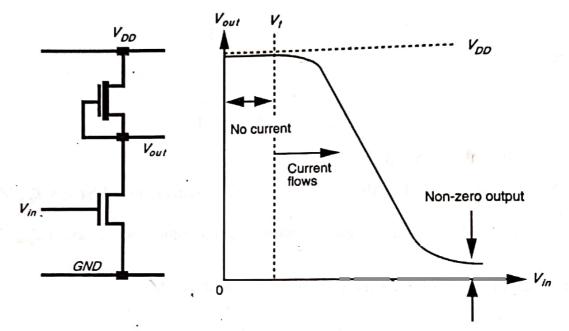

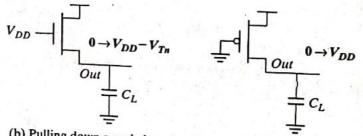

- 2. nMOS depletion mode transistor pull-up (Figure 2.12).

- (a) Dissipation is high since rail to rail current flows when  $V_{in} =$ logical 1.

- (b) Switching of output from 1 to 0 begins when  $V_{in}$  exceeds  $V_i$  of p.d. device.

- (c) When switching the output from 1 to 0, the p.u. device is non-saturated initially and this presents lower resistance through which to charge capacitive loads.

FIGURE 2.12 nMOS depletion mode transistor pull-up and transfer characteristic.

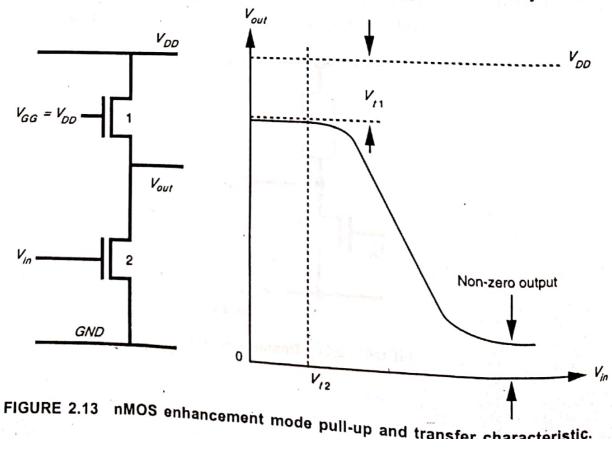

- 3. nMOS enhancement mode pull-up (Figure 2.13).

- (a) Dissipation is high since current flows when  $V_{in} = \text{logical 1} (V_{GG} \text{ is returned to } V_{DD})$ .

- (b)  $V_{out}$  can never reach  $V_{DD}$  (logical I) if  $V_{GG} = V_{DD}$  as is normally the case.

Scanned by CamScanner

17

- (c)  $V_{GG}$  may be derived from a switching source, for example, one phase of a clock, so that dissipation can be greatly reduced.

- (d) If  $V_{GG}$  is higher than  $V_{DD}$  then an extra supply rail is required.

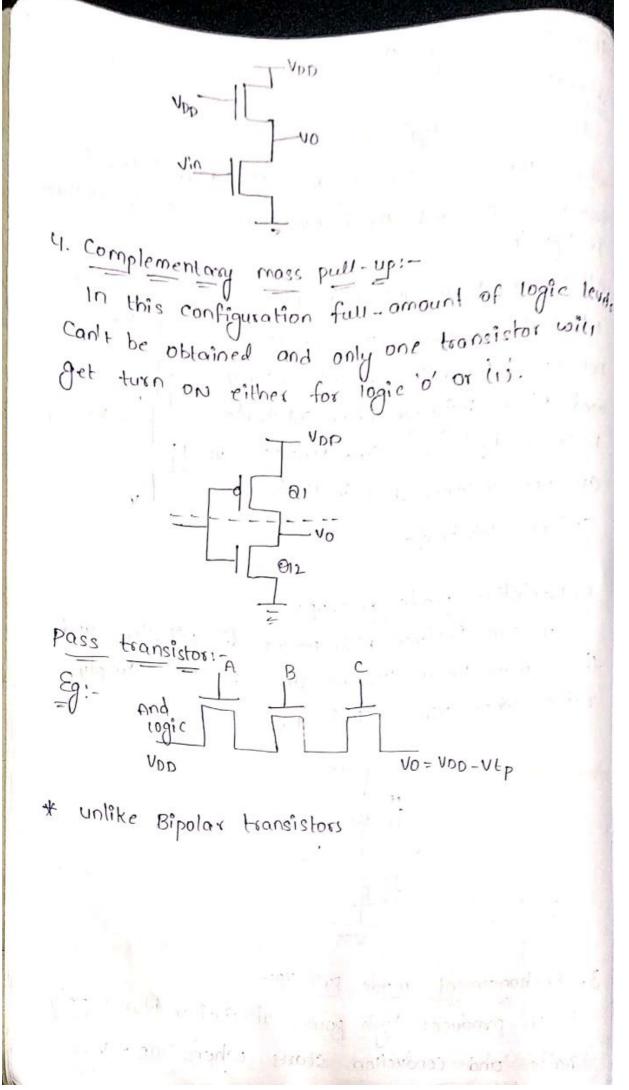

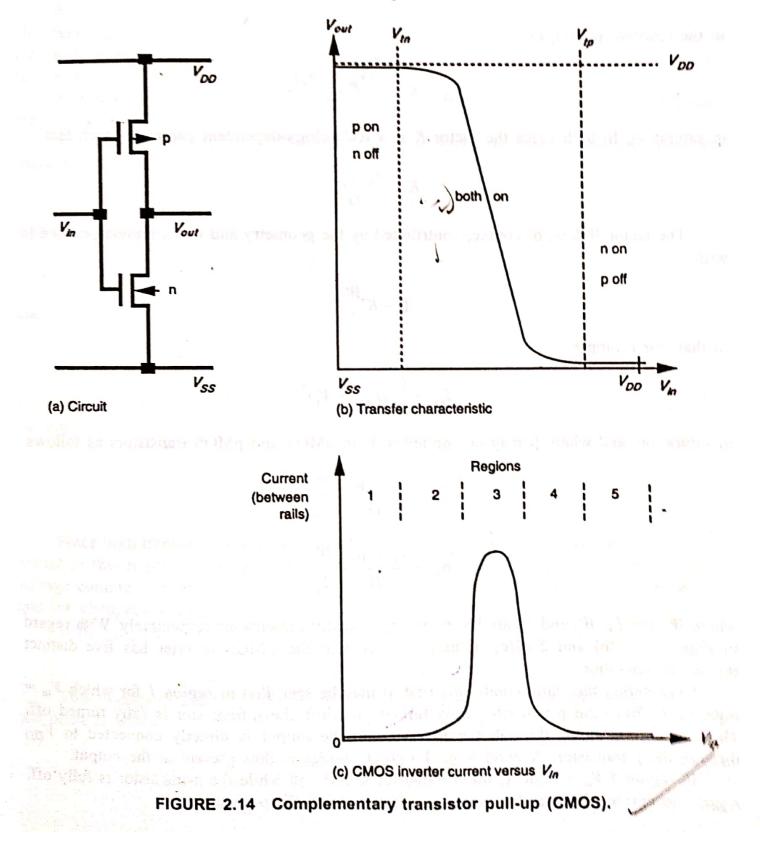

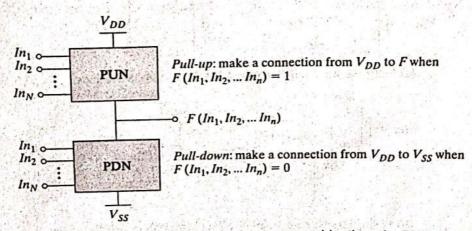

4. Complementary transistor pull-up (CMOS) (Figure 2.14).

- (a) No current flow either for logical 0 or for logical 1 inputs.

- (b) Full logical 1 and 0 levels are presented at the output.

- (c) For devices of similar dimensions the p-channel is slower than the n-channel device.

www.Jntufastupdates.com Scar

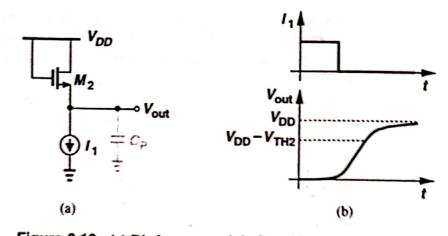

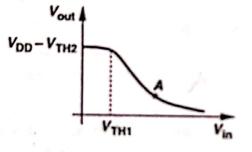

#### 2.10 THE CMOS INVERTER

The general arrangement and characteristics are illustrated in Figure 2.14. We have seen (equations 2.4 and 2.5) that the current/voltage relationships for the MOS transistor may be written

$$I_{ds} = K \frac{W}{L} (V_{gs} - V_t) V_{ds} - \frac{V_{ds}^2}{2}$$

in the resistive region, or

$$I_{ds} = K \frac{W}{L} \frac{(V_{gs} - V_{t})^{2}}{2}$$

in saturation. In both cases the factor K is a technology-dependent parameter such that

$$K = \frac{\varepsilon_{ins}\varepsilon_0\mu}{D}$$

The factor W/L is, of course, contributed by the geometry and it is common practice to write

$$3 = K \frac{W}{L}$$

so that, for example

$$I_{ds} = \frac{\beta}{2} (V_{gs} - V_t)^2$$

in saturation, and where  $\beta$  may be applied to both nMOS and pMOS transistors as follows:

$$\beta_n = \frac{\varepsilon_{ins}\varepsilon_0\mu_n}{D} \frac{W_n}{L_n}$$

$$\beta_p = \frac{\varepsilon_{ins}\varepsilon_0\mu_p}{D} \frac{W_p}{L_p}$$

where  $W_n$  and  $L_n$ ,  $W_p$  and  $L_p$  are the n- and p-transistor dimensions respectively. With regard to Figures 2.14(b) and 2.14(c), it may be seen that the CMOS inverter has five distinct

Considering the static conditions first, it may be seen that in region 1 for which  $V_{in} = \frac{1}{C}$ logic 0, we have the p-transistor fully turned on while the n-transistor is fully turned off. Thus no current flows through the inverter and the output is directly connected to  $V_{DD}$ through the p-transistor. A good logic 1 output voltage is thus present at the output.

In region 5  $V_{in}$  = logic 1, the n-transistor is fully on while the p-transistor is fully off. Again, no current flows and a good logic 0 appears at the output.

#### Scanned by CamScanner

In region 2 the input voltage has increased to a level which just exceeds the threshold voltage of the n-transistor. The n-transistor conducts and has a large voltage between source and drain; so it is in saturation. The p-transistor is also conducting but with only a small voltage across it, it operates in the unsaturated resistive region. A small current now flows through the inverter from  $V_{DD}$  to  $V_{SS}$ . If we wish to analyze the behavior in this region, we equate the p-device resistive region current with the n-device saturation current and thus obtain the voltage and current relationships.

Region 4 is similar to region 2 but with the roles of the p- and n-transistors reversed. However, the current magnitudes in regions 2 and 4 are small and most of the energy consumed in switching from one state to the other is due to the larger current which flows in region 3.

Region 3 is the region in which the inverter exhibits gain and in which both transistors are in saturation.

The currents (with regard to Figure 2.14(c)) in each device must be the same since the transistors are in series, so we may write one of a sufficient series of the same since the same si

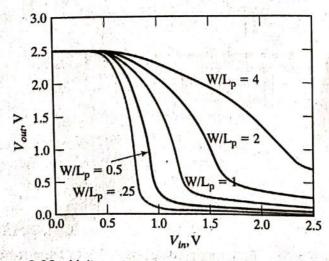

of symmetry when  $V_{out} = V_{in} = 0.5V_{out}$  and  $I_{out} = V_{in} = 0.5V_{out}$  and  $I_{out} = V_{in} = 0.5V_{out}$ . The  $\beta$  ratio is often unimportant in many configurations and in most cases minimum size transistor geometries are used for both n- and p-devices. Figure 2.15 indicates the production in the transfer characteristic as the ratio is varied. The changes indicated in the figure would be for quite large variations in  $\frac{1}{2}(\frac{1}{q}V_{1c}-(\frac{1}{Q}V_{1c}-\frac{1}{q}V_{1c}))(\frac{1}{2}) = \frac{1}{qsb}I_{1b}$  ratio is thus not too critical in this respect.

and

$$I_{dsn} = \frac{\beta_n}{2} \left( V_{in} - V_{in} \right)^2$$

from whence we can express  $V_{in}$  in terms of the  $\beta$  ratio and the other circuit voltages and currents

$$V_{in} = \frac{V_{DD} + V_{ip} + V_{in} (\beta_n / \beta_p)^{1/2}}{1 + (\beta_n / \beta_p)^{1/2}}$$

(2.10)

1 wov

Since both transistors are in saturation, they act as current sources so that the equivalent circuit in this region is two current sources in series between  $V_{DD}$  and  $V_{SS}$  with the output voltage coming from their common point. The region is inherently unstable in consequence and the changeover from one logic level to the other is rapid.

If  $\beta_n = \beta_p$  and if  $V_{in} = -V_{ip}$ , then from equation (2.10).

$$V_{in} = 0.5 V_{DL}$$

This implies that the changeover between logic levels is symmetrically disposed about the point at which

$$V_{in} = V_{out} = 0.5 V_{DD}$$

The MOS transistin can be modeled with varying degrees of complexity However a constituentian of the actual physical construction of the device (as in Figure 1.16) leads to some model.

#### Scanned by CamScanner

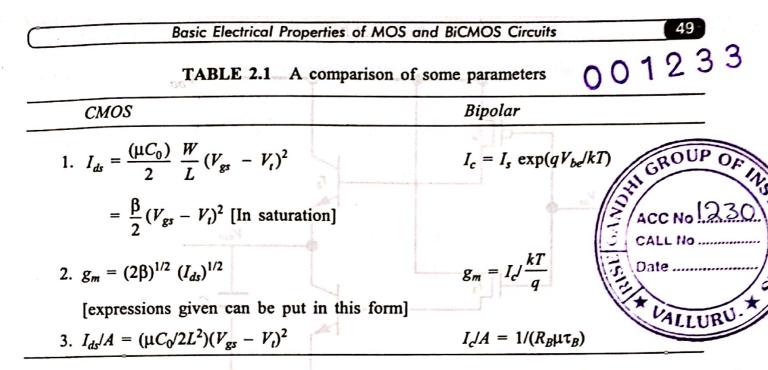

where  $I_{ds}/A$  and  $I_c/A$  are current/area and  $R_B$  is base resistance and  $\tau_B$  is the base transit time (usually in the order of 10-30 ps).

Evaluating, we may see that I/A for bipolar is five times better than that for CMOS. A discussion of the current drive aspects of BiCMOS circuits will be found in Chapter 4 (section 4.8.3).

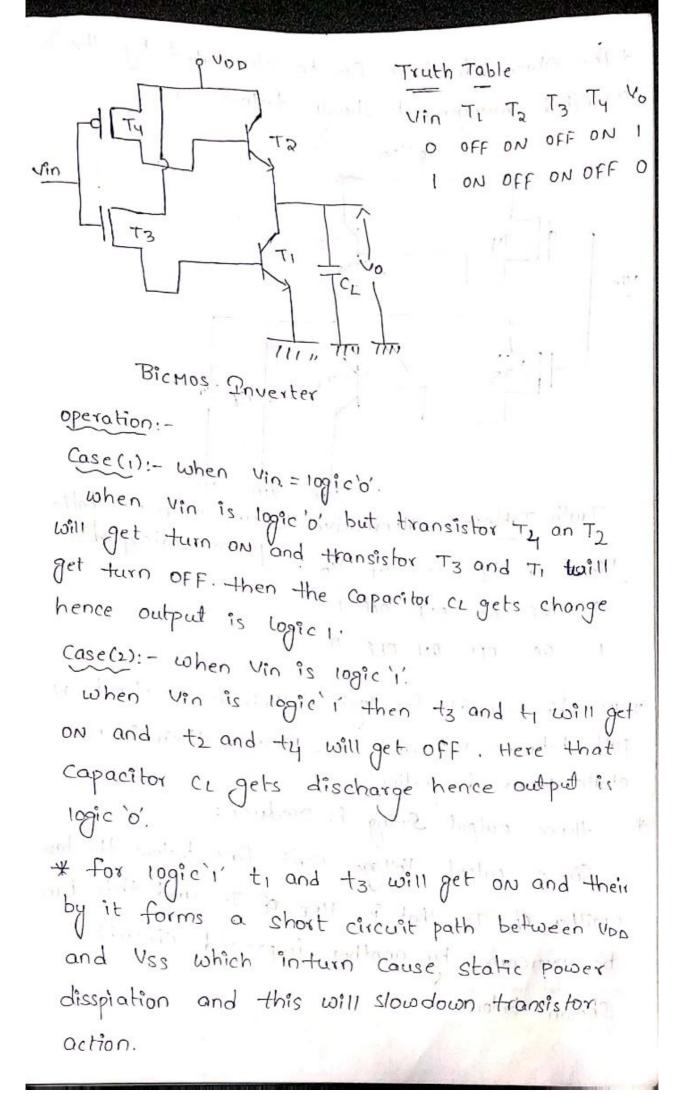

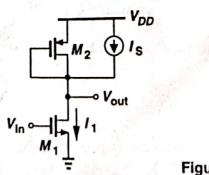

#### 2.12.3 BiCMOS Inverters

As in nMOS and CMOS logic circuitry, the basic logic element is the inverter circuit.

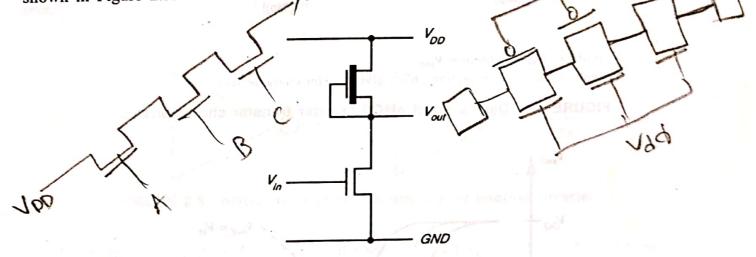

When designing with BiCMOS in mind, the logical approach is to use MOS switches to perform the logic function and bipolar transistors to drive the output loads. The simplest logic function is that of inversion, and a simple BiCMOS inverter circuit is readily set out as shown in Figure 2.17.

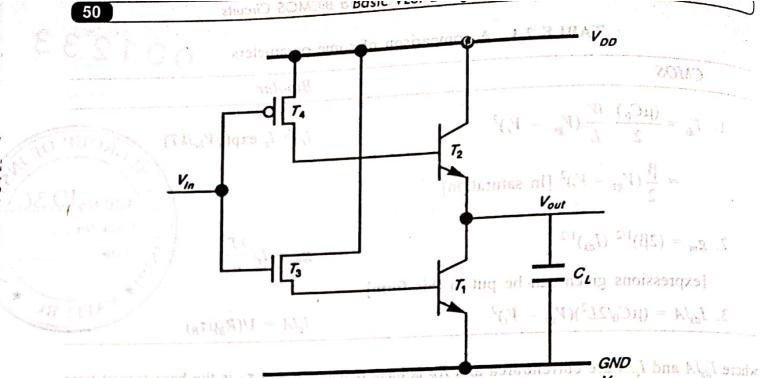

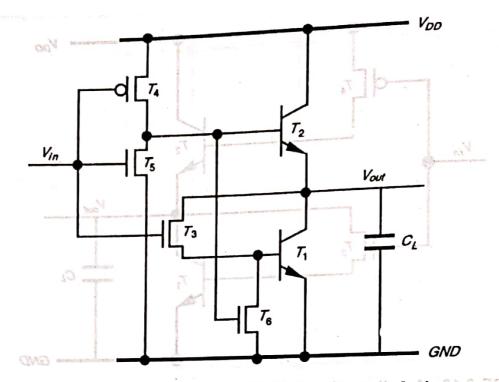

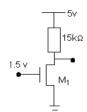

It consists of two bipolar transistors  $T_1$  and  $T_2$  with one nMOS transistor  $T_3$ , and one pMOS transistor  $T_4$ , both being enhancement mode devices. The action of the circuit is straightforward and may be described as follows:

- With  $V_{in} = 0$  volts (GND)  $T_3$  is off so that  $T_1$  will be non-conducting. But  $T_4$  is on and supplies current to the base of  $T_2$  which will conduct and act as a current source to charge the load  $C_L$  toward +5 volts( $V_{DD}$ ). The output of the inverter will rise to +5 volts less the base to emitter voltage  $V_{BE}$  of  $T_2$ .

- With  $V_{in} = +5$  volts  $(V_{DD})$   $T_4$  is off so that  $T_2$  will be non-conducting. But  $T_3$  will now be on and will supply current to the base of  $T_1$  which will conduct and act as a current sink to the load  $C_L$  discharging it toward 0 volts (GND). The output of the inverter will fall to 0 volts plus the saturation voltage  $V_{CEsat}$  from the collector to the emitter of  $T_1$ .

•  $T_1$  and  $T_2$  will present low impedances when turned on into saturation and the load  $C_L$  will be charged or discharged rapidly.

(asually in the order of 10-30 ps).

Fvaluating, we may **retrieve SOMOie Bigmis A iv71.2 BRUDIF** than that for CMOS A discussion of the current drive aspects of BiCMOS circuits will be found in Chapter 4

- The output logic levels will be good and will be close to the rail voltages since  $V_{CEsat}$  is quite small and  $V_{BE}$  is approximately + 0.7 volts.

- The inverter has a high input impedance. another a 20MOIE E.SI.S

- The inverter has a low output impedance.

- The inverter has a high current drive capability but occupies a relatively small area.

- The inverter has high noise margins. Juint of 20MOIA they gaugeed notw

However, owing to the presence of a DC path from  $V_{DD}$  to GND through  $T_3$  and  $T_1$ , this is not a good arrangement to implement since there will be a significant static current flow whenever  $V_{in} = \log i c 1$ . There is also a problem in that there is no discharge path for current from the base of either bipolar transistor when it is being turned off. This will slow down the action of this circuit.

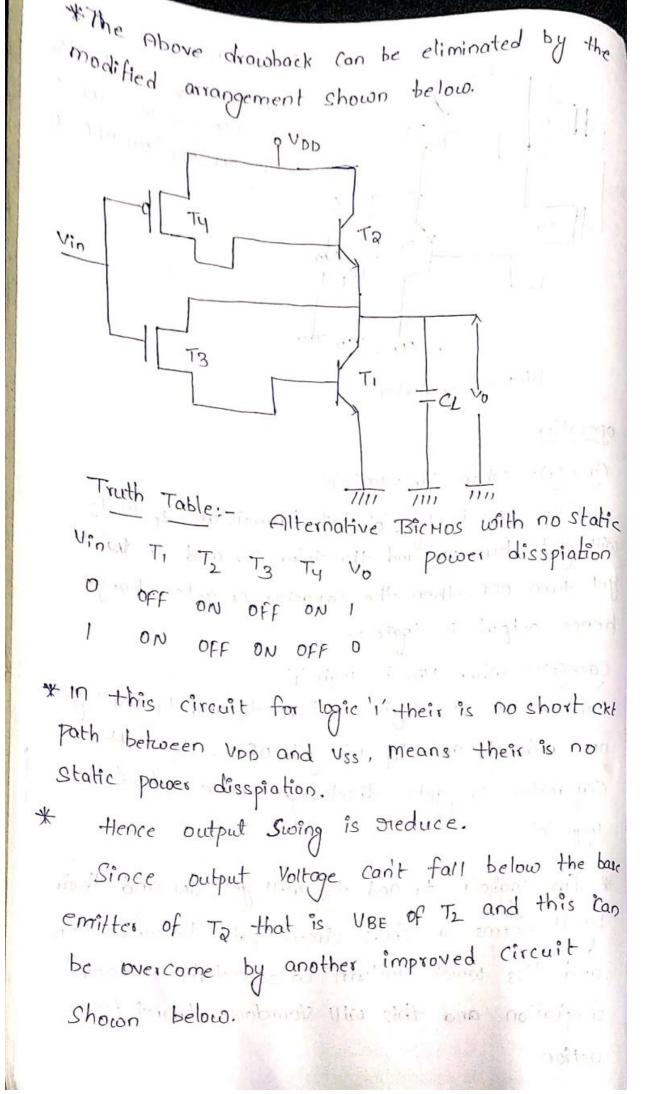

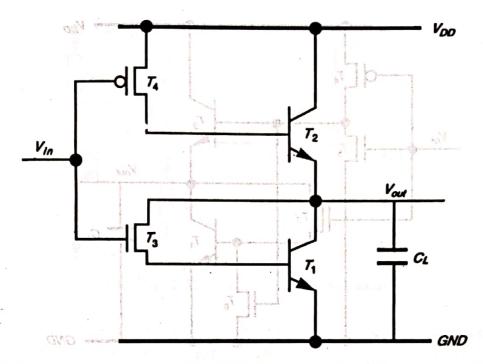

An improved version of this circuit is given in Figure 2.18, in which the DC path through  $T_3$  and  $T_1$  is eliminated, but the output voltage swing is now reduced, since the output cannot fall below the base to emitter voltage  $V_{BE}$  of  $T_1$ .

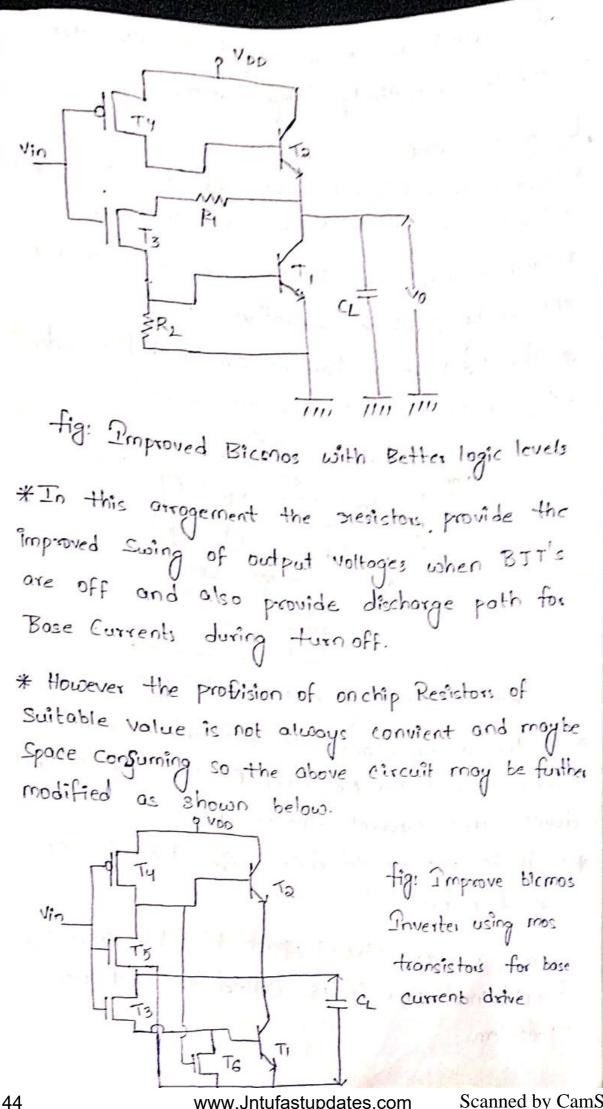

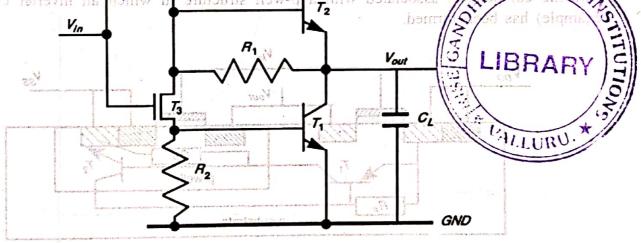

An improved inverter arrangement, using resistors, is shown in Figure 2.19. In this circuit resistors provide the improved swing of output voltage when each bipolar transistor is off, and also provide discharge paths for base current during turn-off.

The provision of on chip resistors of suitable value is not always convenient and may be space-consuming, so that other arrangements—such as in Figure 2.20—are used. In this circuit, the transistors  $T_5$  and  $T_6$  are arranged to turn on when  $T_2$  and  $T_1$  respectively are being turned off.

In general, BiCMOS inverters offer many advantages where high load current sinking and sourcing is required. The arrangements lead on to the BiCMOS gate circuits which will be dealt with in Chapter 5.

22

Basic Electrical Properties of MOS and BiCMOS Circuits

FIGURE 2.18 An alternative BiCMOS inverter with no static current flow. 39001

$\mathcal{V}_{DD}$  and  $\mathcal{V}_{SS}$  with dis**onvertees to actual control during fubrication is necessary to avoid** this problem

Latch-up may be induced by gliches on the supply a bot by incident radiation. The supply a bot by incident radiation. The supply a bot of the supply a bot by the supp

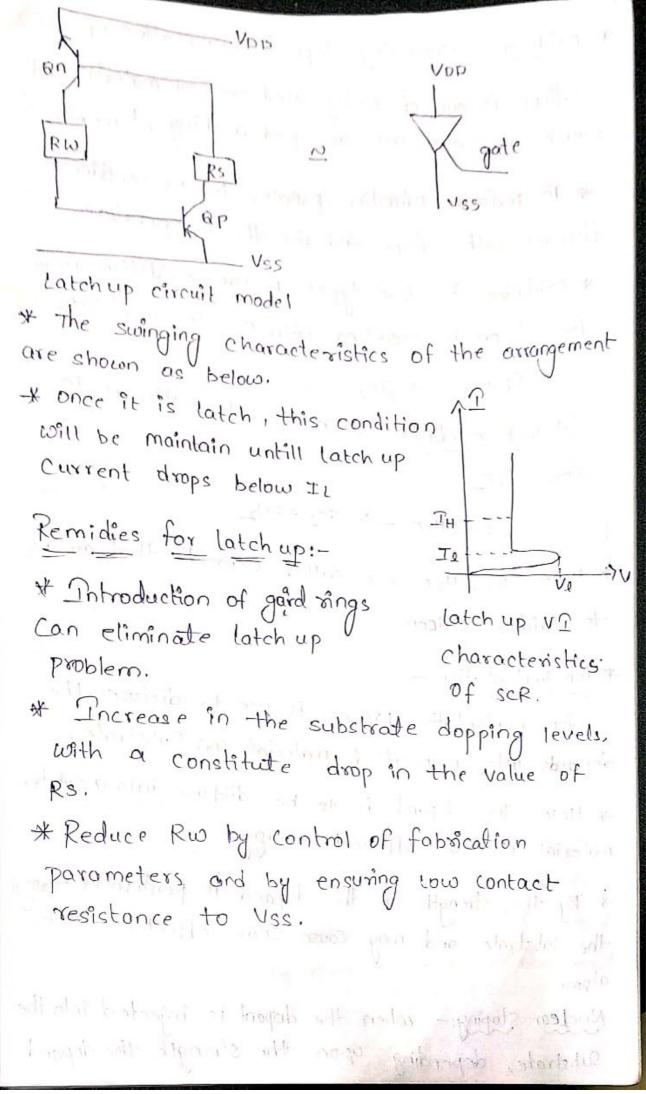

## 2.13 LATCH-UP IN CMOS CIRCUITS TOTAL and I and I

A problem which is inherent in the p-well and n-well processes is due to the relatively large number of junctions which are formed in these structures and, as mentioned earlier, the consequent presence of parasitic transistors and diodes. Latch-up is a condition in which the parasitic components give rise to the establishment of low-resistance conducting paths between

Figure 2.23

51

Scanned by CamScanner

ſ

p

1

FIGURE 2.20 An improved BiCMOS inverter using MOS transistors for base current dischange.

$V_{DD}$  and  $V_{SS}$  with disastrous results. Careful control during fabrication is necessary to avoid this problem.

Latch-up may be induced by glitches on the supply rails or by incident radiation. The mechanism involved may be understood by referring to Figure 2.21, which shows the key parasitic components associated with a p-well structure in which an inverter circuit (for example) has been formed.

FIGURE 2.21 Latch-up effect in p-well structure.

There are, in effect, two transistors and two resistances (associated with the p-well and with regions of the substrate) which form a path between  $V_{DD}$  and  $V_{SS}$ . If sufficient substrate current flows to generate enough voltage across  $R_s$  to turn on transistor  $T_1$ , this will then draw a self-sustaining low-resistance path between the supply rails. If the current gains of the two frames are such that  $\beta_1 \times \beta_2 > 1$ , latch-up may occur. Equivalent circuits are given in Figure 2.22.

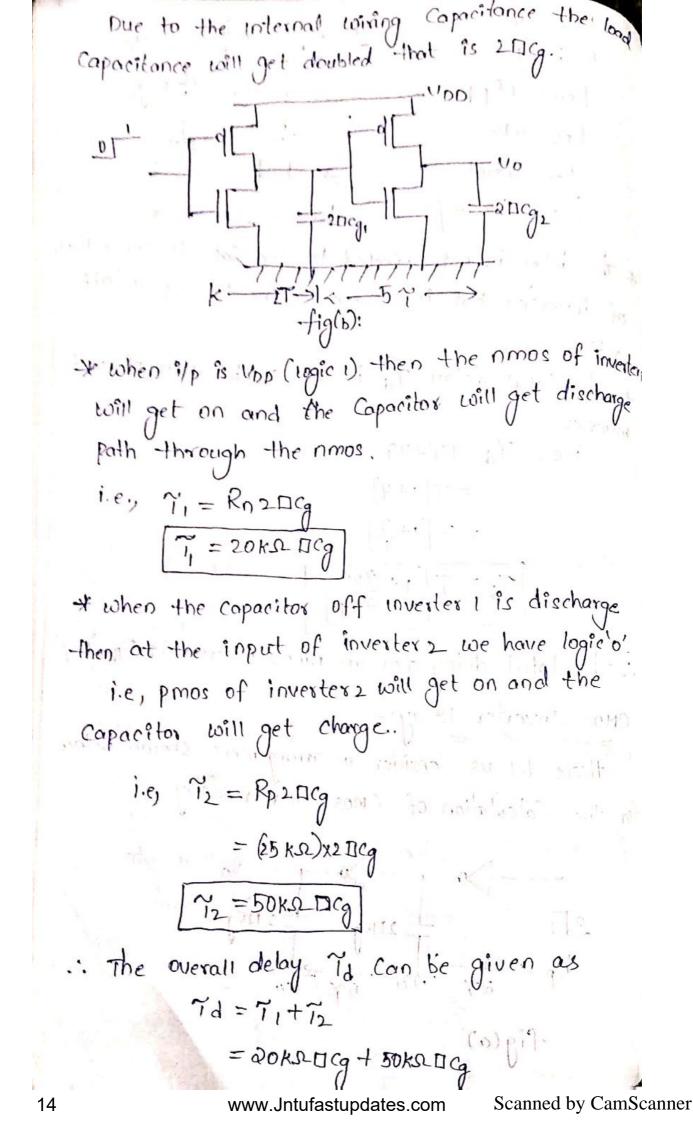

UNIT-I 31/12/18 Basic Circuit Concepts 11 - 102 Sheet Resistance (Rs)1-The concept of sheet Resistance Can be understood by Considering a uniform slab material as shown in the figure below. shall land I per square is independent of 0000 dependent en thickness Longut alt lo so Jud av Peelstance Ba nipoladost inos ar like helow sheet Resistance Model \* so from the given diagram we can say that it is having a length of 12 and width of 'w' and with a 0.03 thickness of t. 0.0y \* The Resistance blw the terminals A and B Can be (notive) given as RAB. µ<-℃  $R_{AB} = \frac{P_{A}}{A}$ cosilisping 15-3100 where P- resistivity 084-31 l-length of the material strizment a Parks (manod) A - Cross-sectional Area rol 212001 -\* for a uniform slab L=w "orxes Chapter WRT RAB = PL/A

1

$R_{AB} = \frac{PR}{2}$ RAB = Pl Hannis times foul.  $= \frac{PA}{\omega E} (\text{uniform slob } l=\omega)$  $R_{AB} = \frac{P}{E}$ The sheet Resistance Rs. can be given as Rs = f \_ per square Note: - The sheet Resistance Rs is independent of Cross-Sectional Area 'A' and dependent on thickness \* some of the typical values of sheet Resistance, different technologies can be tabulated as like be sheet Resistance Hilayerus 101 zum (orbit) 1.2.um 5um 10.0yntoi Metal 0.04 0.03 Diffusion cloament sit with south 20->45 iven at RAG. TRAG F.C. 10->50 (Active) silicid 2->4 Side ptimerizare 15->30 15->100 polysilicon n-transistor poirs 19643 11- 70 221041 - 1 2×104 channel A - Cross-sectional Ar a 2.5×10 Gues 4.5×10 4.5×10 4.5×10 P-transistor channel V/3 1 = C His)

Wheet Resistance Concept Applied to Mois transistors and the sheet Resistance concept can be extended to Here let us Consider a cmos invester as shown invertexs. below." \* The channel Resistance of OF DI 27:27 pmos can be given as ovo 1 Vin-27:27 Rpus = ZRs WKT  $z = \frac{L}{2}$ VSS 112 Rs values Can be =) 27 =1 taken for 5um technology Rpus = 1. Rs 1. Por Convience. = (2.5×104) Lon hRpus = 35 KS210 sandting 1000000. mil \* The Channel Diesistance of Nimos' can be given Par - - - Par as Rpds = Z.Rs  $1 = \frac{1}{16} = \frac{1}{16}$ z = L1.1 = 1.1  $= \frac{27}{27} = 1$ (1'alli = 0.401 -Res = 1. Rs : introval zomen ju somethingt langed no add in Rpds = 10KQ 2617 + 2017 + 2017 + 2017 + 2017 1014.0.401 ... The ON channel Resistance of cmos invester is U HOR RON = Rpus + Rpds = 25k2+10K2 = 35K2

Sheel Resistance Concept Applied for most inverted

The amost inverter is diagramically as shown

below.

The channel Resistance of

depletion model. Can be given as vin

$$(2782)^2$$

Rpus =  $\frac{2}{8}R_3$

$i = \frac{1}{\omega} = \frac{87}{83} = 4$

The Rpus = 4.Rs

$= 44.(2500)^2$

The Channel Resistance of enhancement models

Can be given as

$Z = \frac{1}{\omega} = \frac{27}{87} = 1$

Rpds =  $2\cdot Rs$

$Z = \frac{1}{\omega} = \frac{27}{87} = 1$

Rpds =  $1\cdot Rs$

$= 1(10^4)$

$= 10K\Omega$

The on channel Resistance of Names invester can

be is Ron = Rpus + Rpds

$2500 = 2500$

$2510 + 2010 = 2610$

The sheet Resistance Concept can be extended for transistors, for example Consider two transistors as shown in figure a' and b' shown below. Dete 27 2 WILLIAM DW W SX Or a full of the full LIW 27:27 figure b' figure à' In the above I diagrams figure a is having a length of 27 and a width of 27 and figure b Carriex a length of \$2 with a width of 27. for a fig à the channel. Resistance can be calculated as R=ZRs 1203 ( where = ne Red. "airride 8) and and  $R = 1. (104)^{11}$  suffold to mis =10KSthe channel Resistance for thig b' can be calculated at monthing to envior point off to much the as sigR = Z · Rs mindrate music the mus pould  $z = \frac{L}{\omega} = \frac{81}{27} = 4$ tubulated televit  $R = 4 \cdot Rs$ = 4(104)R = YOKS2

5

Area Capacitance of Layens:,-In the Ic fabrication process, the layers Can be seperated from one another by a oxide Layer (i.e, insulating material) which is acting as dielectric medium between two parallel plates, so their may be a chance of availing Capacitance. The Capacitance c'an be given as In Allin a bac Es la dippol Cit Cit EA Divid o Him is to deput o usines ! Whene E = permitivity and Can be given as coloniated as K= 2 Ro  $e = e_0 e_{ins}$ Co -> Absolute permitivity (or) permitivity of free space. (8.854×102-foroday/meter) Eins -> Relative permitivity = 4 for silicon A = Area of plates lateral D = thickness of Sioz & bounds, all. \* Some of the typical Values of Capacitance for 5µm, our and 1.our technologies Can Are " tabulated below. tabulated below. X - 4. RS (POI)1 = 0.100

|                                                         |                             | Jalue in p<br>5,11m | 2.um -         | m <sup>2</sup> (Jelative Values in<br>brackets) |  |  |  |

|---------------------------------------------------------|-----------------------------|---------------------|----------------|-------------------------------------------------|--|--|--|

| gate to channel 4 (1.0) 8 (1.0) 16 (1.0)<br>capacitance |                             |                     |                |                                                 |  |  |  |

|                                                         | diffusion<br>(active)       | 1 (0.25)            | 1.75<br>(0.20) | 3.75 (0.23)                                     |  |  |  |

| 5.d                                                     | polysilicon<br>to substrate | 0.4 (0.1)           | 0.6 (0.075)    | 0.6 (0.038)                                     |  |  |  |

| -                                                       | Metal 1 to<br>Substrate     | 0.3 (0.075)         | 0·33<br>(0·04) | 0.33 (0.02)                                     |  |  |  |

|                                                         | Metal 2 to<br>Substrate     | 0.2<br>(0·5)        | 0.17<br>(0.02) | 0.17 (0.01)                                     |  |  |  |

|                                                         | Metal 2 to<br>Metal 1       | 0.4<br>(0.1)        | D.5<br>(0.06)  | (0.03)                                          |  |  |  |

|                                                         | Metal2 to<br>polysilicon    | 0.3<br>(0.075)      | 0.3<br>(0.038) | 0.3<br>(0.018)                                  |  |  |  |

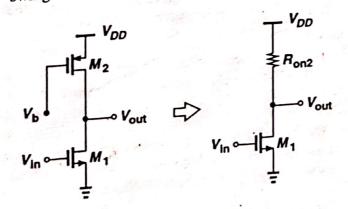

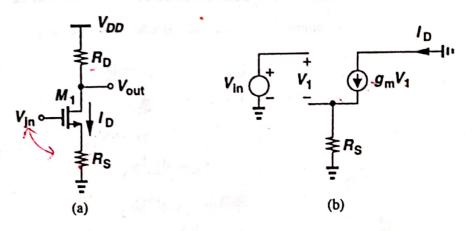

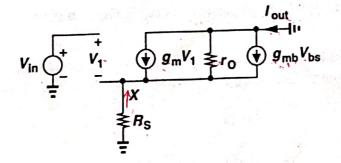

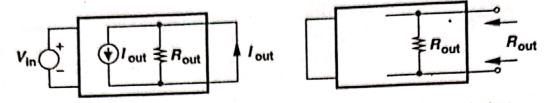

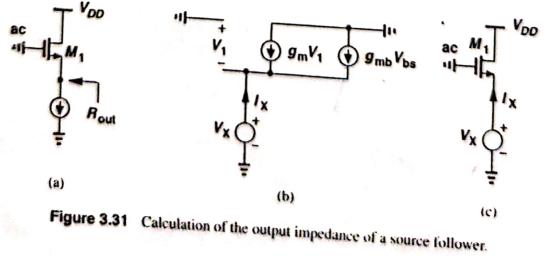

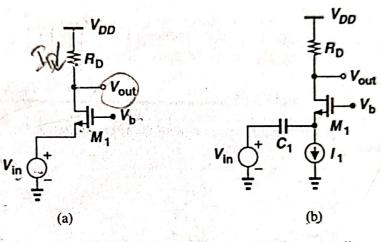

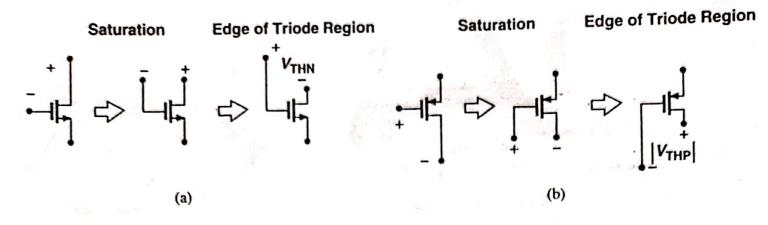

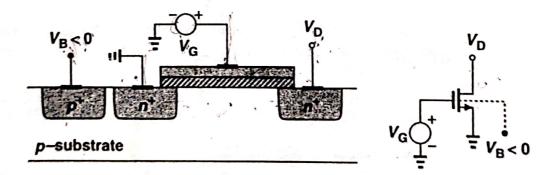

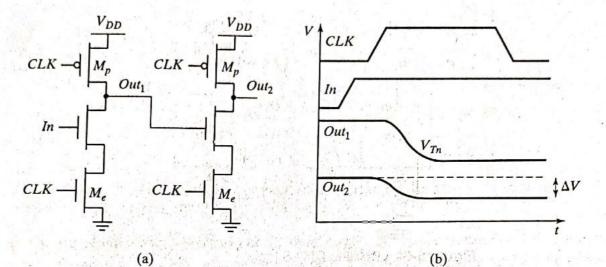

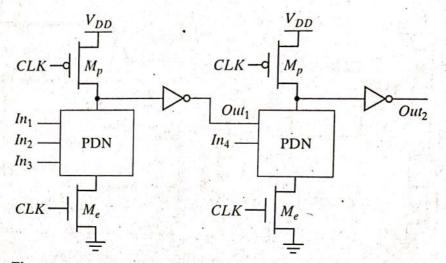

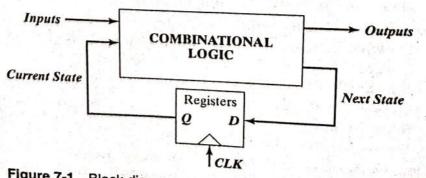

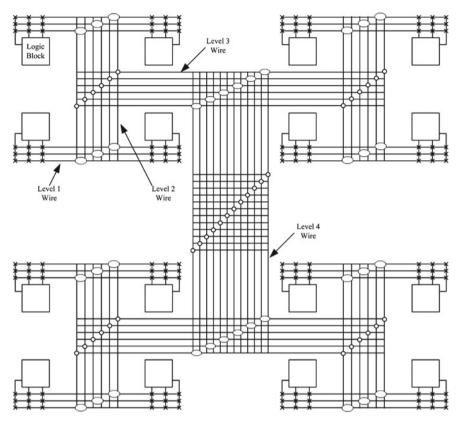

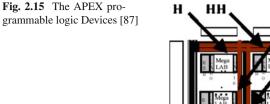

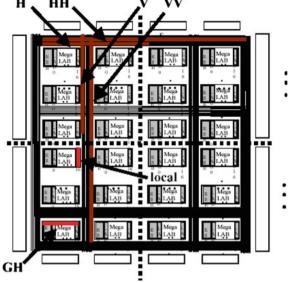

| andard unit of Capacitance (IICg):-                     |                             |                     |                |                                                 |  |  |  |